In der heutigen schnelllebigen Technologielandschaft gewinnen Edge-Computing-Anwendungen zunehmend an Bedeutung. Dabei werden Rechenprozesse nicht mehr zentral in leistungsfähigen Rechenzentren erledigt, sondern direkt dort, wo die Daten entstehen – an der sogenannten „Edge“. Besonders die „exreme Edge“ stellt neue Herausforderungen an die Hardware. Diese umfasst Anwendungen, die extrem niedrigen Energieverbrauch, minimalen Platzbedarf, niedrige Kosten und hohe Flexibilität erfordern, etwa in Smart Textilien, Gesundheitsmonitoring oder Umweltüberwachung. Flexibilität und Energieeffizienz sind dabei der Schlüssel zum Erfolg.

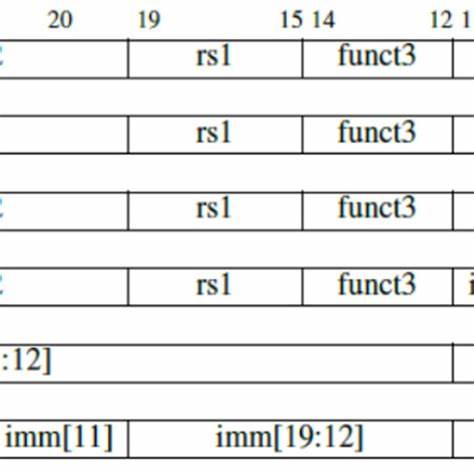

Genau hier setzt die innovative Entwicklung flexibler RISC-V Instruction Subset Prozessoren (RISPs) an – eine maßgeschneiderte Lösung, die sich speziell für extreme Edge-Anwendungen eignet und deren Anforderungen optimal bedient. RISC-V als offene Instruktionssatzarchitektur bietet durch seine Modularität und Offenheit großes Potenzial zur Anpassung und Optimierung. RISPs nutzen diesen Vorteil, indem sie nur jene Instruktionen implementieren, die für eine bestimmte Anwendung oder Anwendungsdomäne tatsächlich erforderlich sind. Dieses Subset wird zu einem maßgeschneiderten Prozessor zusammengefügt, der dadurch nicht nur weniger Ressourcen verbraucht, sondern auch schneller und energieeffizienter arbeitet als ein Standard-RISC-V-Prozessor mit dem vollständigen Instruktionssatz. Ein entscheidender Aspekt bei der Entwicklung von RISPs ist die automatisierte Generierung und Verifikation.

Jede einzelne Instruktion wird als vollständiger, vorverifizierter Hardwareblock behandelt. Das ermöglicht die automatische Zusammensetzung eines Prozessors durch das Zusammenfügen dieser Bausteine. Diese Methode reduziert nicht nur die Entwicklungszeit erheblich, sondern minimiert zudem potenzielle Fehlerquellen und steigert die Gesamtzuverlässigkeit. Der Designprozess ist dabei eng mit einer integrierten Verifikation verzahnt, was für eine hohe Qualität und sichere Funktionalität sorgt. Die Umsetzung der RISPs als flexible integrierte Schaltung (FlexIC) ist ein weiterer Meilenstein.

FlexICs basieren nicht auf herkömmlichen Siliziumsubstraten, sondern Verwendung flexibler Materialien, die etwa in der Elektronik für Kleidung oder tragbare Geräte eingesetzt werden können. Dadurch wird eine neue Klasse von Produkten ermöglicht, die komfortabel, leicht und anpassbar sind. Gerade in der extremen Edge kommen solche Eigenschaften zum Tragen, da dort oft kleinste, unauffällige und dennoch leistungsfähige Systeme benötigt werden. Die Integration von RISPs in FlexICs schafft somit völlig neue Möglichkeiten für innovative Anwendungsgebiete, die mit klassischer Elektronik nur schwer oder gar nicht realisierbar wären. Die Effizienz der RISPs zeigt sich auch in messbaren Vergleichsdaten.

Bei der Synthese von RISPs für verschiedene extreme Edge-Anwendungen sowie für eingebettete Anwendungen aus der bekannten Embench-Benchmark-Reihe konnten deutliche Reduktionen im Energieverbrauch und Platzbedarf erzielt werden. Im Durchschnitt führen die maßgeschneiderten RISPs zu etwa 30 % geringerer Leistungsaufnahme und verkleinertem Flächenbedarf im Vergleich zu einem Standard-RISC-V-Prozessor mit vollem Instruktionssatz. Zudem sind diese RISPs rund 30-mal energieeffizienter als der bislang kleinste bekannte 32-Bit-RISC-V-Prozessor namens Serv. Auch bei der physischen Umsetzung konnte beachtliches Einsparpotenzial nachgewiesen werden: Die RISPs belegten bis zu 21 % weniger Fläche und benötigten bis zu 26 % weniger Energie als Serv. Diese Verbesserungen sind vor allem auf die konsequente Reduktion von Überflüssigem und die darauf abgestimmte Profilierung der Hardware zurückzuführen.

Insgesamt zeigt sich, dass die Kombination aus einer flexiblen Instruktionssubset-Strategie und der Nutzung flexibler elektronischer Materialien eine symbiotische Beziehung bildet, die die Zukunft der Edge-Computing-Hardware maßgeblich prägen kann. FlexICs mit RISPs eröffnen neue Dimensionen an Anpassbarkeit und Nutzungsmöglichkeiten, die weit über die klassischen Anwendungen hinausgehen. Sicherheit und Zuverlässigkeit sind bei der automatisierten Prozessorgenerierung zentrale Punkte. Die lückenlose Verifikation der einzelnen Hardwareblöcke vor ihrer Integration sorgt dafür, dass Fehler frühzeitig erkannt und ausgeschlossen werden. Dies ist besonders wichtig, weil Edge-Anwendungen oft in sicherheitskritischen oder schwer zugänglichen Umgebungen zum Einsatz kommen, wo ein Ausfall schwerwiegende Folgen haben kann.

Die schnelle und fehlerfreie Herstellung maßgeschneiderter RISPs ermöglicht Unternehmen und Entwicklern zudem kürzere Entwicklungszyklen und eine schnellere Markteinführung. Angesichts der rasanten Innovationsgeschwindigkeit im Bereich flexibler Elektronik ist dies ein entscheidender Wettbewerbsvorteil. Ein weiterer Aspekt, der die Bedeutung der RISPs für die Zukunft unterstreicht, ist ihre Nachhaltigkeit. Indem nur die wirklich benötigten Instruktionen implementiert und unnötiger Overhead vermieden wird, minimieren RISPs nicht nur den Energieverbrauch während des Betriebs, sondern reduzieren auch den Materialaufwand bei der Herstellung. In Kombination mit den flexiblen Materialien der FlexICs entsteht so ein Elektronikkonzept, das ressourcenschonend und umweltfreundlich ist.

Das ist besonders wichtig in Zeiten, in denen Elektronikmüll und Energieverbrauch immer stärker in den Fokus geraten. Neben den offensichtlichen Vorteilen in der Hardware eröffnet die RISP-Methodologie auch spannende Perspektiven auf Softwareebene. Da RISPs für spezifische Anwendungen optimiert sind, kann Software ebenfalls schlanker und effizienter gestaltet werden. Firmen und Entwickler können damit speziell zugeschnittene Softwarelösungen kreieren, die perfekt auf die jeweilige Prozessorarchitektur abgestimmt sind. Dies erhöht die Leistungsfähigkeit und spart gleichzeitig Entwicklungszeiten.