In der Welt des Hardware-Designs sind präzise Begrifflichkeiten essenziell, um komplexe Prozesse klar und verständlich zu kommunizieren. Eine besondere Herausforderung stellt dabei der Begriff „Synthesis“ dar, speziell wenn er im Zusammenhang mit dem High-Level Synthesis (HLS) verwendet wird. Das Verständnis und die korrekte Anwendung des Ausdrucks „HLS Synthesis“ sind nicht nur für Forscher und Entwickler von Bedeutung, sondern auch für jene, die an der Schnittstelle zwischen Hardware-Design und Softwareentwicklung agieren. High-Level Synthesis beschreibt einen Prozess, bei dem eine Hardwarebeschreibung nicht in der klassischen Register-Transfer-Level (RTL)-Sprache, sondern auf einer höheren Abstraktionsebene, meist in C oder C++, begonnen wird. Dabei werden softwareähnliche Spezifikationen in ein hardwareverständliches RTL-Format überführt.

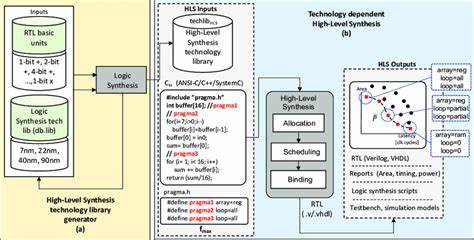

Diese Transformation umfasst zahlreiche Schritte wie Frontend-Parsing, Scheduling, Binding und schließlich die Generierung von Hardwarebeschreibungssprachen wie Verilog oder VHDL. Oft stößt man auf die Herausforderung, wie man diesen Prozess sprachlich präzise benennt. Insbesondere in wissenschaftlichen Arbeiten oder bei detaillierten Beschreibungen kann „Synthese“ an sich missverständlich sein, da im Hardware-Designprozess zwei fundamentale Synthesearten existieren: die High-Level-Synthese und die klassische RTL-Synthese. Während die HLS-Synthese den Weg vom C/C++ Code zum RTL-Design beschreibt, bezieht sich die RTL-Synthese auf die Umwandlung des RTL-Codes in ein Netzlistenformat, das für die physikale Implementierung geeignet ist. Um diese Unterscheidung klar zu machen, hat sich die Bezeichnung „HLS Synthesis“ etabliert.

Obwohl dieses Wortgefüge für Außenstehende redundant erscheinen mag – da „High-Level Synthesis Synthesis“ wortwörtlich doppelt gemoppelt klingt – ist es tatsächlich sinnvoll und pragmatisch. In vielen technischen Kontexten, speziell in der Forschung, werden nämlich beide Prozesse oft im gleichen Satz thematisiert. Beispielsweise ist es üblich, Ergebnisse nach der HLS-Synthese mit denen nach der RTL-Synthese zu vergleichen, um Effizienz, Ressourcenverbrauch oder Timing genauer beurteilen zu können. Die Notwendigkeit der Explizitheit entsteht auch durch die verschiedenen Stadien im HLS-Tool-Flow. In typischen High-Level Synthesis Tools gibt es mehrere standardisierte Abläufe: C-Simulation (csim), RTL Co-Simulation (cosim), die eigentliche HLS-Synthese und schließlich den Export oder die Verpackung der generierten Hardware.

Es ist daher praktisch, mit „HLS Synthesis“ den speziellen Schritt zu benennen, bei dem die hochabstrakte Sprache in einen RTL-Code übersetzt wird. Die Unterscheidung zwischen HLS-Synthese und RTL-Synthese findet zudem in der Design Space Exploration und im maschinellen Lernen große Anwendung. Bei der Design Space Exploration werden verschiedene Parametrisierungen und Architekturoptionen eines Designs untersucht. Hierbei liefert die abschließende HLS-Synthese oft erste Schätzwerte von Ressourcenverbrauch und Timing, die anschließend mit den detaillierteren Ergebnissen der RTL-Synthese validiert oder verglichen werden. Machine Learning Modelle können aus diesen Daten lernen und helfen, optimierte Hardwaredesigns effizienter zu generieren.

Neben der technikbezogenen Präzision wirft die Diskussion um „HLS Synthesis“ auch spannende linguistische und terminologische Fragen auf. In der Forschung wird beispielsweise diskutiert, was der Begriff „Implementation“ genau umfasst und wo die Grenzen zwischen Design, Synthese und physikalischer Umsetzung liegen. Ebenso stellt sich die Abgrenzung zwischen Begriffen wie VLSI, EDA, HDL, DSL und HLS als nicht immer eindeutig heraus. Schließlich hängt vieles davon ab, welchen Kontext man betrachtet und auf welche Abstraktionsebene man sich konzentriert. Der sprachliche Umgang mit Fachterminologie ist auch im akademischen Umfeld nicht trivial.

Einige Kritiker argumentieren, dass Begriffe wie „HLS Synthesis“ stilistisch vermieden werden sollten, da sie sich scheinbar selbst wiederholen – ähnlich bekannten Beispielen wie „ATM Machine“ oder „Chai Tea“. Doch in technischen Disziplinen ist Präzision oft wichtiger als reine Stilfragen. Das mag manchen Schreibstil als repetitiv erscheinen lassen, trägt jedoch maßgeblich zur Klarheit und Missverständnisfreiheit bei. High-Level Synthesis als Technologie hat in den letzten Jahren eine rasante Entwicklung erfahren. Mit immer leistungsfähigeren Algorithmen und komplexeren Hardwarebeschreibungen wird HLS zunehmend zum Standard in vielen Bereichen der Hardwareentwicklung.

Die Möglichkeit, komplexe Systeme direkt aus algorithmischen Beschreibungen zu generieren, spart Entwicklungskosten und verkürzt die Time-to-Market erheblich. Trotzdem bleibt es entscheidend, dass die einzelnen Etappen und Übergänge in diesem Prozess klar voneinander abgegrenzt werden können, wofür Terminologien wie „HLS Synthesis“ unerlässlich sind. Zusammenfassend lässt sich sagen, dass der Begriff „HLS Synthesis“ weit mehr ist als eine redundante Wortkonstruktion. Er bedient sich einer gezielten Differenzierung innerhalb des Hardwaredesignprozesses und verdeutlicht den Unterschied zwischen der Transformation von höher abstrahierten Programmiersprachen zu RTL und der nachfolgenden Umsetzung in physikalische Hardwarestrukturen. Durch diese sprachliche Präzision werden Missverständnisse vermieden und eine klare Kommunikation auch in komplexen multidisziplinären Teams ermöglicht.