In der Welt der Softwareentwicklung und der Prozessorarchitektur spielt die effiziente Handhabung von Speicherzugriffen eine immense Rolle für die Performance. Besonders Load-Store-Konflikte, ein komplexes mikroarchitektonisches Phänomen, können die Ausführungsgeschwindigkeit von Anwendungen drastisch beeinflussen. Diese Konflikte entstehen, wenn Lade- und Speicheroperationen zeitlich oder adressbezogen so aufeinanderfolgen, dass sie interne Puffersysteme der CPU überfordern und dadurch Latenzen verursachen. Ein solches Verhalten ist gerade in Schleifen mit wiederholten Lese- und Schreibzugriffen auf Speicherbereiche, wie etwa bei der Dekodierung komprimierter Geometriedaten, besonders kritisch und wird von vielen Entwicklern unterschätzt. Um die Problematik von Load-Store-Konflikten zu verstehen, ist es zunächst wichtig, die Funktionsweise von Speicherzugriffen auf modernen CPUs genauer zu betrachten.

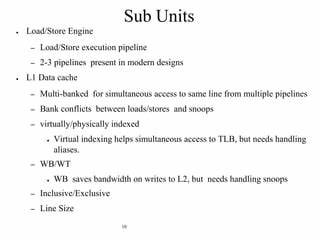

Wenn ein Store-Befehl ausgeführt wird, wird die Schreiboperation nicht unmittelbar in den Cache geschrieben, sondern meist in einem dedizierten Store-Buffer zwischengespeichert. Dies soll verhindern, dass langsame Zugriffe auf Speicherhierarchien das Programm ausbremsen. Die später folgenden Load-Operationen prüfen zunächst diesen Store-Buffer, um festzustellen, ob die angeforderten Daten dort bereits vorliegen. Wird eine Übereinstimmung gefunden, erfolgt eine sogenannte Store-to-Load-Weiterleitung (store-to-load forwarding), bei der die Daten direkt aus dem Store-Buffer gelesen werden, ohne dass die Cache-Hierarchie belastet wird. Diese Technik sorgt für eine enorme Beschleunigung bei engen Load-Store-Abfolgen, indem sie unnötige Speicherzugriffe minimiert.

Hier britzelt jedoch die Komplexität: Wenn eine Load-Operation Daten anfordert, die teilweise von mehreren Stores stammen oder wenn die Speicherzugriffe nicht sauber aufeinander abgestimmt sind, gerät die Store-to-Load-Weiterleitung an ihre Grenzen. In solchen Fällen spricht man von Store-Load-Konflikten. Diese bewirken, dass die CPU den Ladebefehl nicht sofort ausführen kann, sondern warten muss, bis die vorherigen Speicherzugriffe tatsächlich abgeschlossen sind und die Daten im Cache oder im Hauptspeicher verfügbar sind. Das führt zu sogenannten Pipeline-Stalls, also Verzögerungen in der Ausführung, die sich insbesondere bei hochfrequenten Schleifen gravierend auf die Gesamtperformance auswirken. Ein anschauliches Beispiel bietet der Bereich der geometrischen Kompression in Grafik-Engines, speziell beim Dekodieren von Indexpuffern von Dreieckslisten.

Diese Dekodierung ist ein häufiger Flaschenhals bei Rendering-Pipelines und wird intensiv optimiert, um mehrere Gigabyte an Daten pro Sekunde schnell zu verarbeiten. Die zugrundeliegende Datenstruktur, oft eine Art Ringbuffer oder FIFO (First-In-First-Out), speichert dabei Kanten von Dreiecken zur Wiederverwendung. Sowohl Lesen als auch Schreiben passieren in sehr kurzen Abständen auf denselben Speicherbereich. Wenn der Compiler dabei 32-Bit-Teilzugriffe für die FIFO-Elemente generiert, aber diese Lesezugriffe per 64-Bit-Load ausgelesen werden, kommt es zu Store-Load-Konflikten, weil die 64-Bit-Ladebefehle die Daten nicht aus mehreren 32-Bit-Stores konsistent forwarden können. Diese technische Feinheit wurde in der Praxis gut dokumentiert: Neuere Versionen des gcc-Compilers (z.

B. gcc-15) erzeugen aus vermeintlich simplen C++-Quellcodes plötzlich eine solche problematische Lade- und Speicherinstruktionsfolge, die die Dekodierrate auf Zen 4 CPUs merkbar verschlechtert. Interessanterweise führte ein Upgrade auf eine neuere clang-Version beim gleichen Code zu einer erheblichen Leistungssteigerung, da der Compiler Paare von 32-Bit-Stores zusammenführte und ladebare Paare als 64-Bit Leseoperationen generierte, ohne dabei Store-Load-Konflikte hervorzurufen. Diese Erkenntnis zeigt, wie fein abgestimmt Compileroptimierungen auf der Mikroarchitektursebene sein müssen, um spätere Laufzeiteinbußen zu vermeiden. Darüber hinaus ist die Architektur des Zielsystems ausschlaggebend für das Ausmaß solcher Konflikte.

AMDs Zen 4 beispielsweise ist sehr anfällig für diese Form von Store-Load-Konflikten bei SIMD-Operationen mit schmalen Elementen, was den Degradationsgrad in der Praxis um mehrere Zyklen pro Iteration erhöht. Dagegen zeigen Aarch64-Architekturen von Apple mit Cliff-Architektur eine extrem flexible Store-to-Load-Weiterleitung, welche auch teils fragmentierte Datenströme effizient abwickeln kann. Dadurch bleibt die Performance bei ähnlich aufgebautem Code dort trotz vermeintlicher Ineffizienzen high-end. Die Verfügbarkeit von komplexen Instruktionen wie ldp/stp (Load-Pair/Store-Pair) anstelle von einzelnen 32-Bit-Befehlen trägt auch deutlich zur Reduktion von Speicherzugriffskonflikten bei. Die Erkenntnisse aus der Analyse von Load-Store-Konflikten haben weitreichende Konsequenzen für die tägliche Softwareentwicklung, insbesondere bei leistungsrelevanten Systembereichen.

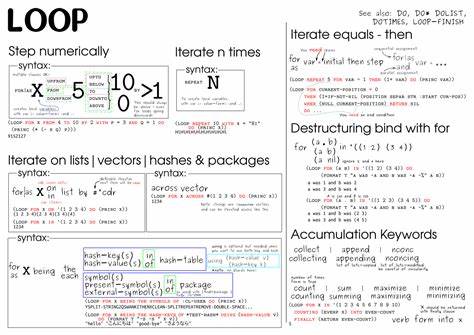

Entwickler, die auf Performance angewiesen sind, sollten das Thema Speicherzugriffsmuster und die Konsequenzen microarchitektonischer Details nicht auf die leichte Schulter nehmen. Ein wichtiges Stichwort ist hier die genaue Beobachtung, wie Compiler aus höherwertigen Programmiersprachen tatsächlich Maschineninstruktionen generieren. Selbst scheinbar gleiche C++-Quellen können durch unterschiedliche Compiler-Versionen oder Compiler-Flags völlig verschiedene Mikroarchitektur-Pfade gehen – mit teilweise dramatischen Folgen für die Laufrendtigkeit. Ein weiterer wichtiger Aspekt betrifft die Gestaltung von Datenstrukturen und die Art ihrer Zugriffe. Häufige Zugriffe auf kleine zusammengesetzte Datentypen, wie etwa ein Array von Paaren aus 32-Bit-Indizes, sind prädestiniert für Store-Load-Weiterleitungsprobleme, wenn die Leseoperationen anders ausgerichtet sind als die Schreiboperationen.

Naheliegend ist hier, Speicherzugriffe in der Schreibtiefe zusammenzufassen, etwa durch die Verwendung von 64-Bit- oder SIMD-Schreibbefehlen anstelle von vielen einzelnen 32-Bit-Schreibern. Ebenso bieten Compilerintrinsics und handoptimierte Assemblersequenzen Optionen, die es erlauben, fein abgestimmte Instruktionsfolgen zu erzeugen, welche Store-Load-Konflikte minimieren. Performance-Profiler und Hardware-Performance-Counter können Entwicklern wertvolle Einblicke verschaffen. Bei AMD-Prozessoren beispielsweise hilft der Zähler Bad_Status_2_STLI (store-to-load interlock), kritische Stellen im Programm zu identifizieren, an denen Store-Load-Konflikte auftreten. Dieses Wissen erlaubt eine gezielte Optimierung an Schlüsselstellen und kann helfen, teure Pipeline-Stalls sichtbar zu machen – ein unverzichtbarer Schritt, um anspruchsvolle Software auf modernen CPUs optimal zu betreiben.

Abschließend lässt sich sagen, dass Load-Store-Konflikte ein komplexes, aber essentielles Detail der Prozessor-Performance darstellen. In Zeiten, in denen Hardware immer schneller wird, aber Software immer komplexere Workloads abbildet, wird die Kenntnis und das Bewusstsein für mikroarchitektonische Besonderheiten zu einem Wettbewerbsvorteil. Entwickler werden gut beraten sein, nicht nur auf hohem Abstraktionsniveau effizient zu programmieren, sondern die Art und Weise, wie ihre Programme auf CPU-Befehlssatzebene umgesetzt werden, genau zu verstehen und zu kontrollieren. Nur so lassen sich versteckte Performancefallen vermeiden, und nur so kann Software heute und in Zukunft das Beste aus moderner Hardware herausholen.