Die Entwicklung des Personal Computers erlebte in den frühen 1980er Jahren einen bedeutenden Wandel mit der Einführung von CPUs, die einen 16-Bit Datenbus unterstützten. Der IBM PC/AT, auch bekannt als IBM 5170, gilt als ikonisches Modell, welches die Ära der 16-Bit Computer eingeläutet und maßgeblichen Einfluss auf die Kompatibilitätsstandards am PC-Markt gehabt hat. Um die komplexen Herausforderungen und Lösungen rund um den 16-Bit Buszugriff dieser Zeit zu verstehen, lohnt sich ein detaillierter Blick auf die Architektur und die dahinterliegenden Hardware-Prinzipien.Die wichtigste technische Neuerung, die CPUs wie den Intel 8086 und 80286 vom früheren 8088 unterschied, war eine Verdopplung der Datenbusbreite von 8 auf 16 Bit. Obwohl dies eine offensichtliche Verbesserung der Datenverarbeitungsrate versprach, brachten die neuen 16-Bit Datenbusse auch einige Herausforderung mit sich, wie zum Beispiel die strikten Anforderungen an die Speicheradressierung, die sogenannten Speicher-Alignment-Regeln.

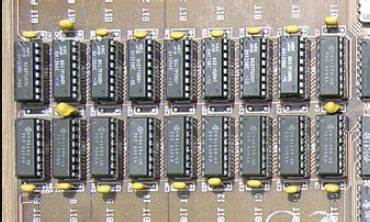

Was heute fast als trivial gilt, war damals ein entscheidender Faktor für die Programmierung und Systemperformance.Speicheralignment bedeutete, dass der Zugriff auf 16-Bit Datenwörter grundsätzlich an gerade und nicht an ungerade Speicheradressen gebunden war. Das liegt an der physischen Art und Weise, wie die Datenbusleitungen und die RAM-Module organisiert waren. Auf der IBM 5170 Hauptplatine waren die RAM-Chips in zwei getrennte, je 8-Bit breite Speicherbänke aufgeteilt, die als High- und Low-Byte-Lanes bezeichnet wurden. Die untersten acht Datenleitungen (D0 bis D7) waren der Low-Bank zugeordnet, die oberen acht (D8 bis D15) der High-Bank.

Damit wurde der Speicherlaufwerkaufbau in zwei gleichwertige Hälften für gerade und ungerade Speicheradressen gesplittet.Interessanterweise war die kleinste Adressleitung des Prozessors, die A0-Leitung, nicht direkt verbunden, um nach den üblichen Erwartungen den exakten Speicherchip anzusprechen. Stattdessen verwendete das System die A1-Adresse als MA0 im Speicheradressierungslogik. Das hatte zur Folge, dass die Speicherchips tatsächlich nur auf gerade Speicheradressen zugreifen konnten. Die Speicherbänke waren also physisch so adressiert, dass die Low-Bank für gerade und die High-Bank für ungerade Bytes verantwortlich war.

Dadurch war ein direkter 16-Bit Zugriff auf ungerade Speicheradressen nicht möglich, weil die Daten dazu auf unterschiedlichen Speicherbänken landen, die nicht simultan angesprochen werden konnten.Das Betriebskonzept des 16-Bit Busses wurde durch das Signal !BHE (Bus High Enable) ergänzt, das vom Prozessor genutzt wurde, um anzuzeigen, ob die oberen 8 Bits des Datenbusses aktiviert werden sollten. Wenn der Prozessor beispielsweise einen 16-Bit Zugriff auf eine gerade Speicheradresse durchführte, war !BHE aktiv und beide Speicherbänke wurden adressiert. Bei einem 8-Bit Zugriff auf eine ungerade Adresse hingegen wurde nur die High-Bank angesprochen, auch wenn !BHE ebenfalls aktiv war. Zusammen mit dem Zustand von A0 konnte das System so unterscheiden, ob es sich um einen 8- oder 16-Bit Zugriff handelte.

Diese Aufteilung und Signalisierung führte zu dem bekannten „Alignment Penalty“-Effekt, also einem Zeitverlust bei ungeraden 16-Bit Speichervorgängen. Beim Versuch, ein 16-Bit Wort an einer ungeraden Adresse zu lesen oder zu schreiben, musste der Prozessor zwei einzelne 8-Bit Zyklen durchführen, da jede Speicherbank separat angesprochen werden musste. Die dadurch entstehenden doppelten Buszyklen und möglicherweise zusätzlichen Wartezustände konnten insbesondere in Schleifen mit vielen unaligned Lese- oder Schreibzugriffen die Systemgeschwindigkeit signifikant beeinträchtigen.Auch im Bereich des BIOS und der ROM-Speicher zeigte sich diese geteilte Struktur. Die BIOS-ROM-Sockel auf dem IBM 5170 Mainboard waren aufgeteilt in zwei Bereiche, die jeweils pro Speicherseite ein Byte lieferten.

Dadurch entstanden zwei getrennte Dateien für übliche BIOS-Emulatoren: eine für gerade und eine andere für ungerade Adressen. Diese Umsetzung spiegelt exakt die Hardwarestruktur wieder und verdeutlicht die kompromisslose Ausrichtung an der 16-Bit Datenbreite und der durch die Hardwarespezifikation erzeugten Adressierung.Neben dem Speicherzugriff war auch die Ein- und Ausgabeschnittstelle der PC/AT-Architektur von der 16-Bit Erweiterung betroffen. Das ISA-Bussystem wurde um eine zweite Datenleitung erweitert, und der !BHE-Signalpegel spielte ebenfalls hier eine wichtige Rolle. Das modulare Design erlaubte so Kompatibilität zu älteren 8-Bit ISA-Erweiterungskarten, während gleichzeitig eine native Unterstützung für 16-Bit Erweiterungskarten eingeführt wurde.

Diese Flexibilität ermöglichte beispielsweise, dass 16-Bit ISA-Karten teilweise auch in 8-Bit Slots betrieben werden konnten – eine bedeutende Kompatibilitätsleistung, die Benutzer von damals sicherlich zu schätzen wussten.Zur Umsetzung dieser unterschiedlich breiten Transfersignale und der Kompatibilitätsanforderungen verwendete IBM auf der 5170 Platine sogenannte PALs (Programmable Array Logic). Diese spezialisierten Chips kontrollierten die Logik zum Beispiel der Buskonvertierung, falls ein 16-Bit Zugriff durch zwei 8-Bit Transfers umgesetzt werden musste. Das PAL-Design war eine effiziente Möglichkeit, komplexe Logic-Funktionen zu verwalten, ohne teure oder komplexe maßgeschneiderte Schaltkreise entwickeln zu müssen. Diese Logik beeinflusste unter anderem das READY-Signal, das vom 80284 Clock Driver zur Taktsteuerung des Prozessors genutzt wurde, um Wartezustände einzufügen und damit korrekte Synchronisation bei zusätzlichen Speicherzyklen zu gewährleisten.

Ein spannendes Detail betrifft den 16-Bit Zugriff an der sogenannten Segmentgrenze im Real Mode. Der 8086 bzw. 8088 kombiniert eine 16-Bit Segmentadresse und einen 16-Bit Offset zu einer 20-Bit Lineadresse. Dabei kann es vorkommen, dass eine 16-Bit Wort-Zugriffsoperation die Grenze des aktuellen Speichersegments überschreitet und somit zwei aufeinanderfolgende Segmente betrifft. Prozessoren wie der 80186 behandelten diese Situation anders als der 8086, indem die Folgebitte an einer höheren Speicheradresse geholt wurden, was zum Lesen über Segmentgrenzen hinaus führte.

Der 80286 führte einen Segment-Überlauf-Fehler aus, wenn ein solcher Zugriff versucht wurde. Dieses Verhalten wurde für Softwareentwickler essentiell, um korrekte Segmentierung und Speicherzugriffe zu gewährleisten und Fehler zu vermeiden.Die Evolution der Speichertechnologie nahm Einfluss auf den 16-Bit Buszugriff. Beispielsweise wurden im AT-Ökosystem früher 30-Pin SIMMs für den Arbeitsspeicher verwendet, die jeweils nur über einen 8-Bit breiten Datenbus verfügten. Für eine vollständige 16-Bit Speicheranbindung mussten zwei Module gleichzeitig installiert werden.

Spätere 72-Pin SIMMs hingegen unterstützten einen 32-Bit Datenbus, und mit fortschreitender Integration entwickeln sich CPUs wie der 386EX, die direkt mit 16-Bit SRAM-Chips kommunizieren konnten, wobei eine kluge Verwendung der zur Verfügung stehenden Selektionssignale wie !BHE und A0/BLE die Hardwaregestaltung deutlich vereinfachte.Diese Historie hat einen nachhaltigen Einfluss auf die moderne Hardwareemulation. Wer die genaue Busaktivität und Timing-Züge von PC/AT-Systemen nachbilden möchte – beispielsweise für Emulatoren wie MartyPC – kommt nicht umhin, das Verhalten von !BHE, die Beschränkungen bei ungeraden Adressen sowie die Auswirkungen auf Wartezustände und Speicherzugriffe nachzubilden. Dafür existentieren mittlerweile akkurat implementierte Testsets, die den Buszustand pro CPU-Zyklus dokumentieren und es Entwicklern erlauben, Hardwareverhalten authentisch zu emulieren.Als Fazit bleibt festzuhalten, dass die 16-Bit Busarchitektur des PC/AT-Systemes mit ihren besonderen Anforderungen an Speicheralignment und der geteilten Datenbankengestaltung ein wichtiges technisches Kapitel der PC-Geschichte geschrieben hat.

Die konsequente Hardwareimplementierung, die Anpassung der Speicherchips und der Einsatz intelligenter Logikbausteine wie PALs zeigen, wie sich technische Herausforderungen durch durchdachte Hardwarekonzepte und Protokolle lösen ließen. Die Auswirkungen dieser Architektur sind nicht nur im historischen Kontext spannend, sondern bieten heute noch wertvolle Erkenntnisse für Hardware-Emulation, Retro-Computing und das Verständnis von Systemdesign bei frühen PC-Generationen.

![Nvidia RTX 2080 Ti: 7 Years from Launch and Still Going Strong but How? [video]](/images/46844F4B-C40B-4340-B877-C77D20705DAF)