Die rasante Entwicklung großer Sprachmodelle (LLMs) hat die Anforderungen an die Rechenleistung in der künstlichen Intelligenz enorm steigen lassen. Besonders bei der Inferenzphase, in der Modelle ihre trainierten Fähigkeiten auf neue Eingaben anwenden, stellt die Matrix-Vektor-Multiplikation (GeMV) einen zentralen Flaschenhals dar. Trotz quantisierter Low-Bit-Modelle, die Speicherbedarf und Rechenleistung reduzieren, bleibt GeMV eine intensive Operation, die die Geschwindigkeit und Energieeffizienz der KI-Systeme begrenzt. Vor diesem Hintergrund eröffnet die jüngst vorgestellte Methode, GeMV direkt in handelsüblichem DRAM auszuführen, neue Wege für effiziente Low-Bit-LLM-Beschleunigung. Die innovative Technologie namens MVDRAM bringt erhebliche Verbesserungen bei Geschwindigkeit und Energieeinsparungen, ohne dass dafür spezielle Hardware benötigt wird.

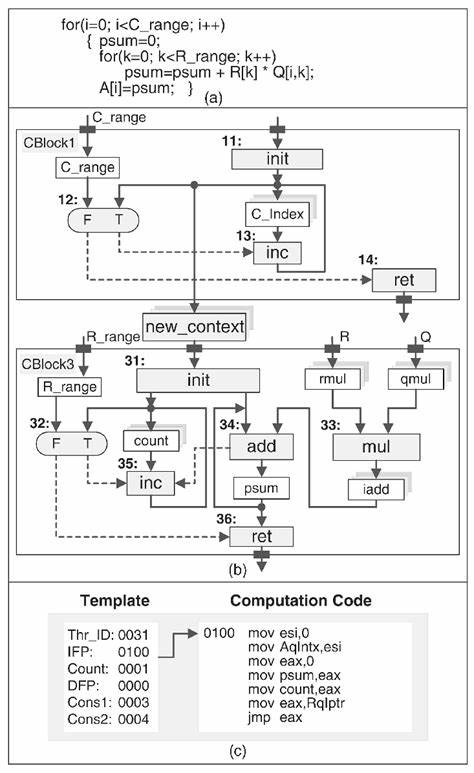

Dadurch verspricht sie eine Demokratisierung fortschrittlicher KI-Anwendungen, indem zahlreiche Endgeräte von einer höheren Leistung profitieren können. Traditionelle Ansätze zur Beschleunigung von Matrix-Vektor-Multiplikationen fokussierten sich auf spezialisierte Hardware oder CPU/GPU-Optimierungen. Während Prozessoren mit wachsender Parallelität und Verbesserungen im Bereich der Quantisierung bei Low-Bit-Modellen Meilensteine erzielten, sind sie oftmals limitiert durch den Speicherzugriff, den sogenannten Bottleneck zwischen Prozessor und Speicher. Das klassische Prinzip, Daten zwischen Prozessor und DRAM hin- und herzubewegen, verzögert die Berechnung und verbraucht mehr Energie, als eigentliche mathematische Operationen. Hier setzt das Konzept des Processing-Using-DRAM (PUD) an.

Die Grundidee besteht darin, Berechnungen direkt im Speicher zu erledigen und dadurch die Latenzzeiten und den Energieaufwand für Datenbewegungen drastisch zu reduzieren. Bisherige PUD-Lösungen verlangten oft Modifikationen am DRAM oder brachten zusätzliche Overheads durch notwendige Vorbereitungen der Daten und aufwändige Nachbearbeitungsschritte mit sich. MVDRAM ist zum ersten Mal eine praktische Implementierung, die auf unveränderten, handelsüblichen DRAM-Modulen basiert und gezielt für Low-Bit-LLMs optimiert wurde. Diese Innovation gelang durch das clevere Ausnutzen der Datenverteilungsmuster und der linearen Eigenschaften der GeMV-Operationen. Durch orchestrierte Zusammenarbeit zwischen Prozessor und DRAM ist es möglich, die vorher notwendigen Zwischenschritte zu eliminieren, die konventionelle PUD-Lösungen verlangten.

Auf diese Weise erhöht MVDRAM die Ausführungsgeschwindigkeit und Energieeffizienz deutlich, ohne die bestehende Speicherinfrastruktur zu verändern. Die experimentellen Evaluierungen auf DDR4-DRAM-Modulen verdeutlichen die Fortschritte: MVDRAM erreicht bis zu 7,29-fache Beschleunigung und eine 30,5-fache Energieersparnis für low-bit GeMV-Operationen, verglichen mit herkömmlichen CPU-basierten Methoden. Auch die gesamte Inferenzkette von Low-Bit-LLMs profitiert von der Technik mit bis zu 2,18-fachem Durchsatz und einer bis zu dreifachen Energieeffizienzsteigerung bei 2-Bit-Quantisierung. Die Vorteile liegen nicht nur in der Geschwindigkeit, sondern sind auch von großer Bedeutung für den Einsatz auf mobilen und eingebetteten Geräten. Diese profitieren oftmals von begrenzten Ressourcen und geschlossenen Netzwerken, in denen energieeffiziente Berechnungen und die Auslagerung von Rechenleistung in den Speicher die Echtzeitfähigkeit und den Autonomiegrad verbessern.

Die Nutzung handelsüblicher DRAM-Module eröffnet zudem eine Perspektive auf Kostenreduktion und breite Anwendbarkeit, da keine neuen spezialisieren Speicherchips oder teure Hardware-Upgrades notwendig sind. Neben den rein technischen Vorteilen wirkt sich die Verlagerung der Rechenlast in den Speicherbereich sehr positiv auf das Design zukünftiger KI-Systeme aus. Die entstehende Synergie zwischen klassischem Prozessor und dynamischem Speicher kann ein Baustein für heterogene Hardwarearchitekturen sein, bei denen spezialisierte Komponenten gezielt ausgewählt und kombiniert werden, um optimale Leistung zu erzielen. Für Low-Bit-LLMs, die wegen quantisierungsbedingter Präzisionseinschränkungen besonders gut für angewandte KI in ressourcenbegrenzten Umgebungen geeignet sind, stellt MVDRAM einen entscheidenden Schritt in Richtung praktischer und nachhaltiger KI dar. Die Forschung zeigt außerdem, dass die bereits existierende Hardwareinfrastruktur in modernen Computern noch nicht ausgeschöpft ist und durch innovative Software- und Firmware-Lösungen zu neuem Leben erweckt werden kann.

Künftige Entwicklungen könnten dieses Prinzip auf höhere Bitraten oder komplexere neuronale Netzwerkoperationen ausweiten und so eine noch umfassendere Beschleunigung und Optimierung ermöglichen. Auch Kombinationen mit anderen Technologien wie Near-Memory-Computing oder Photonic-Computing sind denkbar und könnten zusammen mit MVDRAM neue Bereiche der KI-Beschleunigung erschließen. Für Entwickler, Hardware-Hersteller und Wissenschaftler ist MVDRAM eine spannende Grundlage, die nicht nur das Potenzial für bessere Leistung und Energieeffizienz aufzeigt, sondern auch die Vision zugänglicher, nachhaltiger und skalierbarer KI-Systeme näher rückt. Leistungsstarke Low-Bit-LLMs werden so auf breiter Front einsetzbar, was die Entwicklung intelligenter Anwendungen in unterschiedlichsten Branchen – von der mobilen Medizin über das autonome Fahren bis hin zur Echtzeit-Sprachassistenz – fördern kann. Abschließend lässt sich sagen, dass die Implementierung von Matrix-Vektor-Multiplikationen in handelsüblichem DRAM einen bedeutenden Paradigmenwechsel im Bereich der KI-Hardware darstellt.

Mit MVDRAM zeigt sich eindrucksvoll, wie eine neuartige Nutzung vorhandener Technologien die Grenzen bisheriger Systeme sprengen kann und wegweisende Fortschritte in Geschwindigkeit, Energieverbrauch und Skalierbarkeit ermöglicht. Die Zukunft KI-beschleunigender Hardware könnte somit deutlich flexibler, zugänglicher und effizienter gestaltet werden – eine Perspektive von großer Relevanz für die Industrie und Gesellschaft gleichermaßen.