In der Welt der Softwareentwicklung ist Performanceoptimierung ein komplexes und oft verwirrender Prozess. Entwickler investieren Stunden damit, Code effizienter zu gestalten, lediglich um festzustellen, dass der erhoffte Performance-Gewinn ausbleibt oder sogar gegenteilige Effekte auftreten. Doch gibt es tatsächlich ein universelles Prinzip, das Klarheit in das Wirrwarr bringt? Ein Modell, das alle Low-Level-Codeoptimierungen unter einen gemeinsamen Nenner stellt und uns erlaubt, ihre Wirkung vorhersehbar zu analysieren? Die Antwort lautet ja – das sogenannte „Eiserne Gesetz der Software-Performance“. Dieses Prinzip, ursprünglich aus der Hardware-Architektur bekannt, findet im Software-Bereich eine faszinierende Anwendung und erleichtert das Verständnis für die Mechanismen hinter erfolgreichen oder misslungenen Optimierungen. Das eiserne Gesetz der Performance basiert auf drei Kennzahlen, die zusammen die Ausführungsgeschwindigkeit eines Programms bestimmen: die Anzahl der ausgeführten Maschinenbefehle, die mittlere Anzahl von Taktzyklen pro Befehl und die Dauer eines einzelnen CPU-Takts.

Diese drei Faktoren beeinflussen sich gegenseitig und definieren letztlich die Laufzeit eines Programms. Um die Software-Performance zu verbessern, müssen Entwickler stets an einem oder mehreren dieser Stellschrauben drehen – entweder indem sie die Anzahl der benötigten Instruktionen reduzieren, den Durchsatz der Befehlsausführung erhöhen oder die Taktzeit verkürzen. In der Praxis bedeutet das, dass intelligente Optimierungstechniken stets aus einer bewussten Abwägung zwischen diesen drei Größen bestehen. Nehmen wir das Beispiel der Schleifenentfaltung. Dabei wird ein Schleifenrumpf mehrfach in einer Schleife zusammengefasst, sodass weniger Schleifensteuerbefehle ausgeführt werden müssen.

Das reduziert die Gesamtzahl der Anweisungen signifikant. Gleichzeitig ermöglicht es eine höhere Parallelität für den Prozessor, der mehrere unabhängige Instruktionen gleichzeitig ausführen kann – man spricht von einer Steigerung der Instruction Level Parallelism (ILP). Dadurch kann der Prozessor pro Taktzyklus mehr Befehle abarbeiten (erhöhte Instructions Per Cycle, IPC) und beschleunigt so den Programmablauf deutlich. Allerdings birgt schleifenentfaltung auch Risiken. Wird der Schleifenrumpf zu groß, steigt der Bedarf an CPU-Registern erheblich.

Sind diese erschöpft, lagern Compiler Werte in den Arbeitsspeicher aus – sogenannte Register Spills – was die Zugriffszeiten drastisch erhöht und den Leistungsgewinn schmälern kann. Zudem wächst mit der Loop-Größe der Code, was Druck auf den Instruktionscache ausübt. Falls wichtige Instruktionen aus dem Cache verdrängt werden, sinkt die Befehlsversorgungsrate der CPU, was die parallele Ausführung schwächt und somit den IPC erneut verringert. Dieser Trade-off zeigt beispielhaft, wie das eiserne Gesetz der Performance Entwickler zwingt, zwischen gegensätzlichen Effekten zu balancieren. Eine weitere sehr verbreitete Optimierung ist die Funktionsinlining.

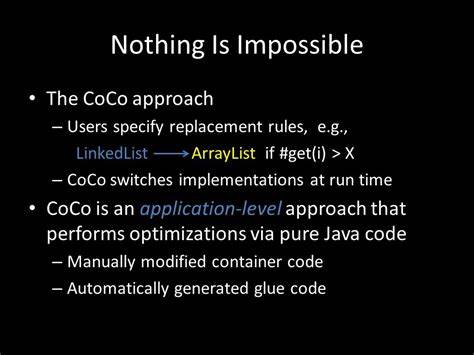

Dabei werden Funktionsaufrufe zur Compilezeit in den Code integriert, sodass die Overheadkosten des Aufrufs – wie das Anlegen des Stackframes, das Speichern von Registern oder Rücksprungbefehle – entfallen. Auf den ersten Blick ist dies ein simpler und effektiver Trick, der die Anzahl an Maschinenbefehlen reduziert und die Ausführung beschleunigt. Aber auch hier gibt es Fallstricke: Inlining vergrößert den Code und kann ebenfalls zu erhöhter Registerbenutzung führen, was im schlimmsten Fall wiederum Register Spills provoziert und Instruktionscacheprobleme verschärft. Darüber hinaus öffnet Inlining dem Compiler Tür und Tor für context-sensitive Optimierungen, wie das Propagieren bekannter Parameter, was netterweise oft den Instruktionsumfang zusätzlich verringert und so den Performance-Gewinn vergrößert. Auch SIMD-Vektorisierung ist ein Paradebeispiel für eine leistungsfähige Optimierungsmethode, die sich gerade in datenintensiven Anwendungen durchgesetzt hat.

Hierbei führt der Prozessor eine einzelne Instruktion aus, die gleichzeitig auf mehrere Datenpunkte angewandt wird – also „Single Instruction Multiple Data“. Diese Technik reduziert drastisch die dynamische Anzahl ausgeführter Befehle, da mit jedem SIMD-Befehl mehrere Werte verarbeitet werden. Die IPC steigt somit, weil mehr Rechenoperationen pro Takt erledigt werden können. Auf der negativen Seite kann die Taktfrequenz des Prozessors durch den erhöhten Energiebedarf von SIMD-Befehlen sinken, insbesondere bei breiten SIMD-Erweiterungen wie AVX-512. Dies erhöht die Taktzeit und vermindert damit den Performance-Vorteil.

Ferner vergrößert SIMD oft die Codegröße und erhöht die Komplexität der Registerverwaltung, was analog zu den vorherigen Optimierungen zu den bekannten Herausforderungen wie Cache-Druck und Register Spills führt. Auch die Optimierung von Verzweigungsvorhersagen hat eine enorme Bedeutung für die Performance. Moderne Prozessoren setzen auf spekulatives Ausführen und versuchen durch branch prediction Fehlvorhersagen zu minimieren. Ein Fehlschlag in dieser Vorhersage führt dazu, dass der CPU-Pipeline Instruktionen verworfen werden müssen, was kostspieligen Stillstand und sinkende IPC zur Folge hat. Durch Umstrukturierung von Code, z.

B. durch Branch Elimination oder Anwendung bedingungsloser Befehle, kann dieser Flaschenhals entschärft werden. Allerdings entstehen oft mehr Befehle und eine niedrigere ILP, da bedingungslose Methoden meist Abhängigkeitsketten verursachen. Das bedeutet, je besser der ursprüngliche Branch vorhersagbar ist, desto weniger lohnt sich eine Umstrukturierung, da die IPC-Einbußen den gewonnenen Vorteil überwiegen. Hier zeigt sich, wie wichtig das Verständnis der zugrundeliegenden Iron-Law-Kennzahlen für kluge Entscheidungen ist.

Nicht zuletzt müssen auch Cache-Misses betrachtet werden. Der Datencache spielt eine zentrale Rolle bei der Performance, da Speicherzugriffe die langsamsten Operationen im System sind. Ein Cache-Miss führt zu langen Verzögerungen, da Daten aus dem Hauptspeicher geladen werden müssen und dabei wertvolle CPU-Ressourcen blockiert werden. Optimierungen, die die Cache-Lokalität verbessern, wie Datenlayout-Transformationen oder Software-Prefetching, können die IPC deutlich erhöhen. Der Nachteil liegt meist in einem Anstieg der Instruktionsanzahl, bedingt durch zusätzlichen Pointer-Arithmetik oder Kontrollstrukturen.

Wiederum gilt die Frage: Wie verhalten sich Instruction Count, IPC und Taktzeit insgesamt zueinander? Das Eisenhafte Gesetz der Performance ermöglicht es, die Wirkung all dieser Optimierungen systematisch zu verstehen und abzuwägen. Es verhindert den Tunnelblick auf isolierte Faktoren wie bloße Reduktion der Instruktionsanzahl oder vermeintlich einfache Verkürzung von Ausführungswegen. Vielmehr lenkt es den Blick darauf, wie die drei zentralen Größen dynamischer Instruktionscount, IPC und Taktzeit zusammenspielen und sich gegenseitig beeinflussen. Für Softwareentwickler bedeutet dies eine deutlich bessere Planung und Analyse von Performanceverbesserungen. Werkzeuge wie „perf“ geben mittlerweile gezielt Metriken zu diesen Größen aus, sodass Änderungen nachvollziehbar beurteilt werden können.

In der Praxis zeigt sich zudem, dass oft genau die Kombination aus sorgfältiger Auswahl, messbarer Einflussnahme auf diese Parameter und Vermeidung von Nebeneffekten den Unterschied macht. Abschließend lässt sich festhalten, dass das eiserne Gesetz der Performance eine universelle Brille bietet, mit der fast alle Low-Level Optimierungen betrachtet und rational verstanden werden können. Es ersetzt nicht den Blick auf algorithmische Verbesserungen oder generelle Architekturfaktoren, schafft jedoch einen robusten Orientierungsrahmen für die komplexe Welt der Mikrooptimierungen – und macht aus einer potenziellen Blackbox eine nachvollziehbare Systematik. So können Entwickler die Wirkung optimierter Codepfade besser einschätzen, ihre Ressourcen effizient einsetzen und letztlich qualitativ hochwertige, performante Software schaffen.

![iPadOS 26 Window Management On Small Screens: iPad mini and 11in Pro [video]](/images/FF508E6E-29E5-44A4-AD1A-4C05C07ECA9E)