Die stetige Weiterentwicklung der digitalen Logiksynthese ist eine zentrale Herausforderung in der Halbleiterindustrie und der Hardwareentwicklung. Mit der zunehmenden Komplexität moderner Schaltkreise steigt auch die Notwendigkeit für leistungsfähige Methoden, die strukturabhängige Optimierungen effizient und skalierbar umsetzen können. In diesem Kontext gewinnt die Gleichheitssättigung als aufstrebendes Optimierungsverfahren zunehmend an Bedeutung, das durch seine einzigartige Herangehensweise neue Möglichkeiten in der Technologieabbildung und Schaltkreisresynthese eröffnet. Ein besonders vielversprechender Beitrag in diesem Forschungsfeld ist die Entwicklung von E-morphic, einem skalierbaren Framework zur Gleichheitssättigung, das speziell zur strukturellen Exploration in der Logiksynthese konzipiert wurde. Die Technologieabbildung oder Technology Mapping bildet einen essenziellen Schritt in der Logiksynthese, bei dem eine abstrakte logische Beschreibung eines Schaltkreises in eine konkrete Implementierung mit vorgegebenen Bauelementen übersetzt wird.

Die Qualität des finalen Schaltkreises – gemessen an Kriterien wie Fläche, Verzögerung und Energieeffizienz – hängt dabei maßgeblich von der zugrundeliegenden Schaltkreisstruktur ab, die vor dem eigentlichen Mapping vorliegt. Häufig finden vor dem Technologieabbildungsschritt technologieunabhängige Optimierungen statt, deren Ziel es ist, die Schaltkreisstruktur zu verbessern und somit eine Basis für hochwertige Implementierungen zu schaffen. Traditionelle Optimierungsverfahren stoßen hier allerdings schnell an ihre Grenzen, insbesondere wenn es darum geht, das riesige Lösungsspektrum möglicher Schaltkreisvarianten systematisch zu erkunden und strukturelle Bias zu vermeiden. Gleichheitssättigung stellt in diesem Zusammenhang eine revolutionäre Methodik dar. Sie basiert auf der Idee, durch das sukzessive Anwenden von Äquivalenzregeln eine umfassende Sammlung von logisch äquivalenten Schaltkreisvarianten in Form eines sogenannten e-Graphs zu erzeugen.

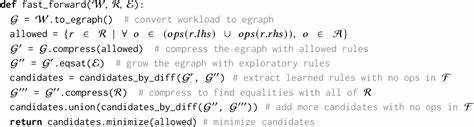

Dieser e-Graph repräsentiert somit einen Raum verschiedener Schaltkreisstrukturen, welche alle funktional identisch sind. Die Herausforderung liegt darin, aus diesem umfangreichen Raum eine optimale Schaltung mit den gewünschten Eigenschaften zu extrahieren, ohne dabei durch die exponentielle Größenzunahme der Varianten überwältigt zu werden. Hier setzt E-morphic an und präsentiert eine maßgebliche Verbesserung der Gleichheitssättigung im Bereich der Logiksynthese. Durch gezielte Innovationen wie die direkte Umwandlung von e-Graphen in Schaltkreise, die systematische Beschneidung des Lösungsraums und den Einsatz von Simulated Annealing als heuristische Extraktionsstrategie gelingt es E-morphic, sowohl die Skalierbarkeit als auch die Effizienz des Optimierungsprozesses signifikant zu steigern. Diese Maßnahmen verhindern, dass der Optimierungsprozess durch die Komplexität des e-Graphs ausgebremst wird, und ermöglichen es, die strukturelle Vielfalt der Schaltkreise aktiv und gezielt zu nutzen.

Ein weiterer entscheidender Vorteil von E-morphic liegt in der Gleichzeitigkeit der strukturellen Exploration und der Resynthese. Während herkömmliche Technologien oft sequenziell und auf festgelegten Mustern basierend arbeiten, erlaubt der Ansatz von E-morphic eine parallele Untersuchung verschiedenartiger Schaltkreisstrukturen, wodurch eine tiefere und breiter gefächerte Optimierung möglich wird. Dies reduziert nicht nur die strukturelle Verzerrung, die in traditionellen Syntheseverfahren häufig auftritt, sondern eröffnet auch ungeahnte Potenziale für die Verfeinerung von Schaltkreisen hinsichtlich Fläche und Performance. Die Praxisrelevanz dieses Verfahrens ist durch umfangreiche Experimente auf großen Benchmark-Schaltkreisen des EPFL-Testsatzes eindrucksvoll belegt. Im Vergleich zum derzeitigen Stand der Technik, beispielsweise optimierten Verzögerungsflüssen im etablierten ABC Framework, erreicht E-morphic beeindruckende Einsparungen von durchschnittlich mehr als zwölf Prozent in der Schaltkreisfläche sowie über sieben Prozent in der Verzögerungsreduktion.

Solche Verbesserungen sind für Entwicklungsingenieure von großem Interesse, da sie direkte Auswirkungen auf die Herstellungskosten, Leistungsaufnahme und letztlich die Wettbewerbsfähigkeit der Produkte haben. Darüber hinaus zeigt der Ansatz vielversprechende Perspektiven für zukünftige Forschungsrichtungen. Die Kombination von Gleichheitssättigung mit fortschrittlichen Extraktions- und Heuristikmethoden könnte das Fundament für noch umfassendere Optimierungen bilden, die nicht nur auf logischer Ebene, sondern auch auf physikalischer Ebene des Schaltkreisentwurfs Anwendung finden. Ebenso eröffnet die Skalierbarkeit des Ansatzes Möglichkeiten, ihn auf sehr große und komplexe Designs anzuwenden, die in modernen System-on-Chip-Architekturen üblich sind. Die Integration von E-morphic beziehungsweise ähnlichen Gleichheitssättigungsframeworks in bestehende Werkzeugketten der Logiksynthese und Hardwareentwicklung könnte somit die Effizienz und Qualität der Entwurfsprozesse revolutionieren.