Die rasante Weiterentwicklung von Künstlicher Intelligenz (KI) und neuronalen Netzwerken stellt Hightech-Ingenieure vor immense Herausforderungen hinsichtlich Rechenleistung, Energieverbrauch und Integration. Traditionelle von-Neumann-Architekturen stoßen gerade bei Machine-Learning-Operationen an physikalische Grenzen, da der Datenverkehr zwischen Speicher und Prozessor einen enormen Flaschenhals darstellt. Compute-In-Memory (CIM) Technologien versprechen, diese Limitierungen zu durchbrechen, indem Rechenoperationen in den Speicherarrays selbst stattfinden. In diesem Kontext präsentiert sich SPIKA als ein moderner, energieeffizienter Hybrid-Makro, der CMOS-Schaltkreise mit Resistive RAM (RRAM) kombiniert und zeitdomänenbasierte Signalcodierung nutzt, um eine außergewöhnliche Leistung bei niedrigem Stromverbrauch zu erzielen. Entwickelt in einem etablierten 180-nm-CMOS-Prozess bietet SPIKA einen pragmatischen und skalierbaren Ansatz zur Beschleunigung von Multiply-Accumulate (MAC) Operationen, die das Herzstück moderner neuronaler Netzwerke bilden.

Im Kern adressiert SPIKA das klassische Problem des sogenannten von-Neumann-Flaschenhalses, indem es Datenbewegungen zwischen Verarbeitung und Speicher drastisch minimiert. Konventionelle Systeme sind durch den Energie- und Zeitaufwand geprägt, der für das Verschieben großer Datenmengen zwischen Recheneinheiten und Speicherchips entsteht. SPIKA hingegen nutzt den programmierbaren Widerstand von RRAM-Zellen, um neuronale Netzwerkgewichte direkt im Speicher zu speichern. Die tatsächliche Vektormatrix-Multiplikation (VMM) wird analog in der zeitlichen Domäne ausgeführt, während digitale Eingaben über Pulsweitenmodulation (PWM) codiert und in analoge Ströme umgewandelt werden. Das innovative Herzstück des SPIKA-Designs ist sein einzigartiger Signal-Domänen-Übergang, der ohne energieintensive Datenkonverter auskommt.

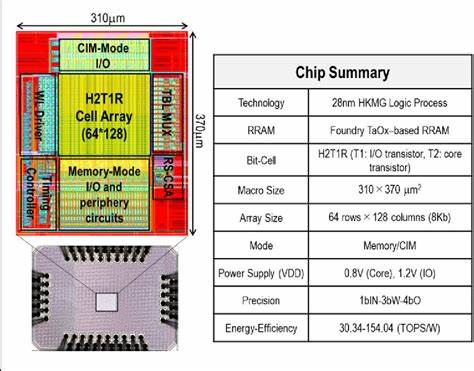

Digitale Eingabesignale werden dazu als PWM-Zeichen dargestellt, die auf RRAM-Zellen angewandt werden, um diese in analog fließende Ströme zu verwandeln. Diese Ströme werden anschließend in einem akkumulierten Wert in einem simplen Kapazitätsspiegel-Leseverfahren zusammengeführt. Besonders bemerkenswert ist das 'Clicking-Mechanismus', bei dem Kapazitäten in den Spalten bei Erreichen eines Schwellenwertes zurückgesetzt werden, und die Anzahl der Rücksetzungen in digitaler Form erfasst wird. Dadurch entfallen teure und stromintensive Analog-Digital-Wandler (ADCs) und Digital-Analog-Wandler (DACs), die typischerweise bei anderen RRAM-basierten CIM-Lösungen einen großen Anteil am Gesamtenergieverbrauch ausmachen. Die Architektur von SPIKA umfasst eine 64×128 RRAM-Crossbar mit einer Abwandlung des bekannten 1T1R-Zellenkonzepts, in der jede Zelle aus einem Transistor (als Zugangsschalter) und einer RRAM-Speicherzelle besteht.

Die Eingänge sind auf 4 Bit ausgelegt, die Gewichte sind ternär (positiv, negativ und null) kodiert, und die Ausgänge besitzen eine 5-Bit-Auflösung. Durch die Platzierung positiver und negativer Gewichte in benachbarten Spalten und die gemeinsame Nutzung eines einzigen Zählers für deren Differenz werden Subtraktionsschritte direkt im digitalen Zähler integriert. Dies vermeidet zusätzliche Komplexität, spart Fläche und minimiert den Energiebedarf. Das Design berücksichtigt zudem die nichtlinearen Eigenschaften von RRAM-Zellen, die sonst zu Genauigkeitsproblemen führen können. Durch die Wahl von Lese- und Arbeitsspannungen nahe 0,1 V (für den niedrigen Widerstandszustand) und 0,2 V (für den hohen Widerstandszustand) kann SPIKA diese Nichtlinearitäten vermindern und stabile lineare Berechnungen erzielen.

Die Kapazitäten in den Spalten werden während der Rechenphase linear entladen und über eine präzise gesteuerte Stromquelle linear aufgeladen, um die Genauigkeit des Systems sicherzustellen. Das Zusammenspiel dieser Analog-Digital-Interaktionen macht das System für Anwendungen mit mittlerer Präzision besonders prädestiniert. Die operative Taktfrequenz von SPIKA liegt dank der optimierten CMOS-Peripherieschaltungen bei 500 MHz, wodurch eine nahezu verlustfreie und schnelle VMM-Berechnung gewährleistet wird. Die gesamte VMM-Operation wird in lediglich 60 ns durchgeführt, was SPIKA zur idealen Lösung für Echtzeit-Inferenz auf Edge-Geräten macht. Die Kombination aus hoher Geschwindigkeit und reduzierter Leistungsaufnahme resultiert in einer Spitzenleistung von 1092 GOPS (Giga Operationen pro Sekunde) und einer herausragenden Energieeffizienz von 195 TOPS/W (Tera Operationen pro Watt im bit-normalisierten Betrieb).

Diese Werte setzen SPIKA an die Spitze vergleichbarer Technologien auf dem Markt, vor allem wenn man bedenkt, dass der Chip in einem weniger dramatisch skalierten 180-nm-Prozess gefertigt wurde. Ein weiterer entscheidender Vorteil liegt in der Flexibilität und Skalierbarkeit der Architektur. SPIKA ist optimiert für Anwendungen mit 4-Bit-Eingaben und 5-Bit-Ausgaben – ein Kompromiss zwischen Leistungsfähigkeit und Komplexität, der auch mit verfügbaren KI-Modellen wie CNN und DNN gut harmoniert. Ziele zukünftiger Weiterentwicklungen umfassen die Erweiterung auf Multi-Core-Designs, um größere Netzwerke abzubilden, sowie die Erforschung von multi-bit RRAM-Technologie, um Gewichte mit höherer Präzision zu speichern und die Skalierbarkeit des Systems zu optimieren. Neben der beeindruckenden Energieeffizienz überzeugt SPIKA auch durch seine Robustheit gegenüber Prozessvariationen, Temperaturschwankungen und RRAM-Gerätevariabilitäten.

Umfangreiche Simulationen zeigen, dass durch eine anpassbare Steuerung externer Spannungs- und Stromquellen die Leistung in verschiedenen Umgebungen stabil bleibt. Die eingesetzte ternäre Gewichtscodierung ermöglicht es zudem, Mehrwert aus einfachen zweistufigen RRAM-Zuständen zu ziehen, was die Integration in aufkommende RRAM-Materialien und -Technologien erleichtert. Der gegenüber bisherigen Konzepten drastisch reduzierte Bedarf an hochauflösenden Analog-Digital-Wandlern und Digital-Analog-Wandlern bringt nicht nur Energie- sondern auch Flächeneinsparungen. In der Praxis entspricht dies einer um etwa 22 % gesenkten Leistungsaufnahme bei gleichzeitig 6 % kleineren Flächenanforderungen verglichen mit dem bekannten ISAAC-Konzept, das als Benchmark im Bereich RRAM-basierter CIM gilt. Dabei wurden diese Verbesserungen trotz des Einsatzes älterer Fertigungstechnologien erzielt, was für ein großes Potenzial bei weiterer Prozessskalierung spricht.

Die Software-Seite des SPIKA-Konzepts ist ebenfalls nicht außer Acht zu lassen: Die Kombination aus digitaler Pulsweitenmodulation und ternärer Gewichtscodierung passt ideal zu gängigen quantisierten neuronalen Netzwerken, die gerade im Bereich Embedded-KI und Edge-Computing zunehmend Beachtung finden. Modelle mit binären oder ternären Gewichten können ohne umfangreiche Hardwareänderungen auf SPIKA implementiert werden, während die Zeitkodierung der Eingaben eine effiziente Ressourcennutzung sicherstellt. Die innovative „Clicking“-Mechanik, bei der die Kapazitäten in den Spalten schrittweise entladen und bei Erreichen eines Schwellwerts zurückgesetzt werden, ist ein Beispiel für eine intelligente Mischung aus analogen und digitalen Schaltungen. Diese Hybridisierung minimiert die Komplexität der Ausleseschaltungen und ermöglicht eine natürliche Subtraktion von Gewichten inklusive negativer Werte direkt im Zähler, was bei konventionellen CIM-Architekturen oft nur durch aufwendige Digitalisierungs- und Subtraktionsprozesse erfolgt. Insgesamt positioniert sich SPIKA als ein richtungsweisendes Konzept, das die mechanischen Begrenzungen klassischer Compute-Architekturen elegant umgeht und zugleich eine Brücke schlägt zwischen den Stärken analoger RRAM-Matrizen und digitaler CMOS-Logik.

Die Kombination macht es besonders interessant für den Einsatz in ressourcenbeschränkten Systemen wie IoT-Geräten, mobilen Robotern oder Embedded-Systemen, für die Energieeffizienz und Platzbedarf oft entscheidende Faktoren sind. Zusammenfassend beweist SPIKA, dass ein hybrider Ansatz mit zeitdomänenbasierter Signalverarbeitung und ternärer Gewichtscodierung nicht nur theoretisch überzeugend ist, sondern sich in realen CMOS-Fertigungstechnologien praktikabel umsetzen lässt. Mit einer brillanten Mischung aus Innovation und pragmatischem Hardwareengineering stellt SPIKA einen wichtigen Schritt zur Umsetzung energiesparender, leistungsfähiger KI-Beschleuniger der nächsten Generation dar. Zukünftige Entwicklungen und Optimierungen werden diesen Trend weiter vorantreiben und das Potenzial dieser Technologie für verschiedenste Anwendungsbereiche voll ausschöpfen.