Die kontinuierliche Weiterentwicklung von Hardwaredesignmethoden ist essenziell, um den immer höheren Anforderungen der Halbleiterindustrie gerecht zu werden. Dabei spielt die Wahl der passenden Hardware Description Language (HDL) eine entscheidende Rolle. Veryl Hardware Description Language, kurz Veryl, positioniert sich als moderne und effiziente Alternative zu SystemVerilog. Die Sprache zeichnet sich durch eine gezielte Optimierung der Syntax, bessere Lesbarkeit, umfassende Entwicklerunterstützung und besonders durch eine enge Kompatibilität mit bestehenden SystemVerilog-Projekten aus. Diese Eigenschaften machen Veryl zu einem vielversprechenden Werkzeug für Ingenieure und Entwickler, die sowohl Produktivität als auch Codequalität verbessern möchten.

Veryl basiert auf SystemVerilog und übernimmt dessen bewährte Konzepte, bietet jedoch durch eine vereinfachte und auf Logikdesign zugeschnittene Syntax zahlreiche Vorteile. Die Sprache fokussiert sich darauf, die typische Komplexität von SystemVerilog zu reduzieren, ohne dabei auf die Leistungsfähigkeit zu verzichten. Dadurch erleichtert Veryl den Einstieg für SystemVerilog-Experten, sorgt für eine höhere Synthesizierbarkeit und sichert konsistente Simulationsergebnisse. Die Anpassungen der Syntax zielen darauf ab, den Designprozess übersichtlicher und somit fehlerärmer zu gestalten. Gleichzeitig sorgen sie für eine verkürzte Entwicklungszeit und verbessern die Wartbarkeit des Codes.

Ein herausragendes Merkmal von Veryl ist die umfassende Interoperabilität mit SystemVerilog. Bei vielen Projekten besteht aufgrund jahrzehntelanger Entwicklungsarbeit ein großer Bestand an SystemVerilog-Modulen. Veryl wurde so konzipiert, dass es eine nahtlose Integration ermöglicht – sowohl in Form von Teilersetzungen existierender Komponenten, als auch durch die Generierung gut lesbaren SystemVerilog-Codes vom Veryl-Kode aus. Dies ist besonders vorteilhaft, da Entwickler ohne kompletten Systemwechsel auf Veryl-Features setzen oder Altprojekte schrittweise modernisieren können, ohne umfangreiche Codekonvertierungen vornehmen zu müssen. Der Fokus auf Produktivität spiegelt sich in der umfangreichen Toolunterstützung wider, die Veryl mitbringt.

Zu den Entwicklungs-Tools gehören Paketmanager, Build-Systeme und Echtzeit-Diagnosewerkzeuge, die in gängigen Editoren wie Visual Studio Code, Vim oder Emacs integriert sind. Automatische Codevervollständigung und automatische Formatierung gehören ebenso zur Standardausstattung. Die Echtzeit-Überprüfung erkennt Fehler wie undefinierte oder ungenutzte Variablen bereits während der Codeeingabe – ein wichtiger Faktor für die Qualitätssicherung und die Steigerung der Entwicklungsgeschwindigkeit. Darüber hinaus unterstützt Veryl eine integrierte Testfunktion, mit der sich Testcode in SystemVerilog oder cocotb direkt einbetten und über Veryl-Befehle ausführen lässt. Dies fördert die enge Verzahnung von Entwicklung und Verifikation innerhalb einer einheitlichen Sprache.

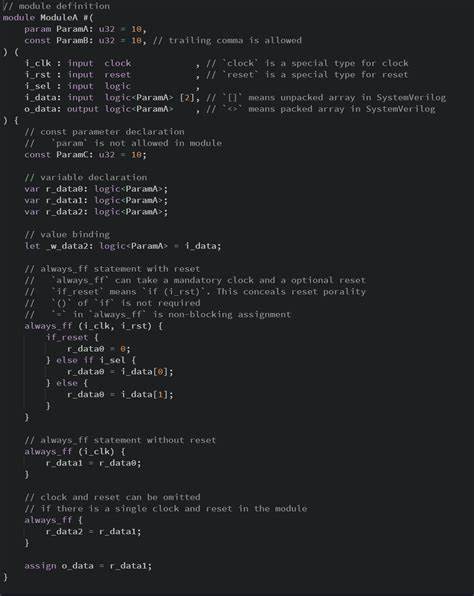

Die Syntax von Veryl bringt einige moderne und praktische Sprachfeatures mit, die den Alltag eines Hardwareentwicklers erleichtern. Zum Beispiel erlaubt Veryl Trailing Commas bei Parameter- und Portlisten, was im Wesentlichen unübersichtliche Änderungen vermeidet und Versionierung übersichtlicher gestaltet. Eine weitere nützliche Eigenheit ist die Abstraktion von Clock- und Reset-Signalen. In Veryl ist es nicht notwendig, die Polarität von Clocks oder Resets im Code festzulegen; diese werden vielmehr zur Build-Zeit spezifiziert. Dadurch unterstützt Veryl die Generierung von Code, der sowohl für ASICs mit asynchronem Reset als auch für FPGAs mit synchronem Reset verwendet werden kann – ohne Anpassung des eigentlichen HDL-Codes.

Veryl setzt zudem auf Klarheit durch die Verwendung einzelner Namespaces für Enum-Varianten. Dies verhindert mögliche Namenskonflikte, die in SystemVerilog bei umfangreichen Modulen und Bibliotheken häufig auftreten. Auch bei der Bitverkettung (Concatenation) wird die Lesbarkeit gesteigert, da Wiederholungen explizit mit einem repeat-Operator geschrieben werden und somit komplexe geschachtelte Konstruktionen einfacher zu verstehen sind. Die Einführung von If- und Case-Expressions anstelle herkömmlicher ternärer Operatoren erhöht die Verständlichkeit, insbesondere bei umfangreichen Auswahlstrukturen. Ein weiteres Merkmal, das besonders bei komplexeren Designs von Vorteil ist, sind die Range-basierten Schleifen, sogenannte Range-based for, inside und outside.

Diese erlauben es, Bereiche mit Halboffen- oder Geschlossenen Intervallen präzise und lesbar zu definieren. So können Indizes oder Wertebereiche komfortabel durchlaufen oder überprüft werden, was die Codequalität und Wartbarkeit spürbar steigert. Veryl bietet auch umfassende Funktionalitäten zur Modularisierung und Strukturierung. Module, Interfaces und Packages können mit Parametern ausgestattet werden, wobei der Einsatz von Generics zur Codewiederverwendung beiträgt. Anders als bei rein parametrisierten Modulen lassen sich bei Veryl ebenfalls Funktionsparameter, Typen und sogar Modulnamen generisch definieren.

Dies führt zu einem deutlich flexibleren und vor allem saubereren Design, da duplizierte Codeteile vermieden werden und die Designs leichter erweiterbar bleiben. Die Sprache unterstützt benannte Blöcke, was die Variablensichtbarkeit im Code streng begrenzt und somit eine sauberere Trennung von Logikteilen ermöglicht. Diese benannten Blöcke dienen auch der besseren Dokumentation und Debugbarkeit im gesamten Entwurf. Im Bereich der Abstraktion und Lesbarkeit sind auch letzte Details gut gelöst. So gibt es den ‚let‘-Befehl, mit dem Werte direkt bei der Variablebindung berechnet werden.

Dies erlaubt einen prägnanteren Code und reduziert Fehlerpotential bei der Initialisierung von Variablen. Der Umgang mit komplexen Reset-Logiken wird durch die integrierte Unterstützung für clk- und reset-spezifische Syntax erleichtert und reduziert den Aufwand bei Änderungen der Reset-Polarität oder Synchronität. Die Sichtbarkeitskontrolle von Modulen wird bei Veryl ebenfalls explizit über das ‚pub‘-Keyword gesteuert. Damit lassen sich interne Implementierungen vom öffentlichen Interface klar abgrenzen, was die API-Konsistenz verbessert und gleichzeitig eine automatische Dokumentation unterstützt. Solche Features sind essenziell für größere Projekte mit mehreren beteiligten Teams und externen Bibliotheken.

Ein Überblick über konkrete Codebeispiele zeigt den modernen, schlanken Stil von Veryl. In Module-Definitionen werden etwa Parameter und Ports in einer klar strukturierten und syntaktisch kurzen Form deklariert. Die Clock- und Reset-Deklaration ist prägnant, da sie die eigentliche Polarity oder Synchronität abstrahiert. Auch Reset-Logik innerhalb von always_ff-Strukturen ist mit intuitive if_reset-Bedingungen gelöst, wodurch der Code lesbarer und weniger fehleranfällig wird. Interface-Definitionen ermöglichen außerdem selektive Sichtbarkeit durch Modports, welche flexibel Master- und Slave-Schnittstellen abbilden können.

Zusammengefasst bringt Veryl Hardware Description Language eine Reihe von Innovationen und Optimierungen mit, die nicht nur den Einstieg erleichtern, sondern auch die Qualität und Effizienz im gesamten Hardwaredesignprozess steigern. Insbesondere die Kombination aus moderner Syntax, Interoperabilität zu SystemVerilog, hervorragender Entwicklungsunterstützung und klarer Struktur macht Veryl zu einem überzeugenden Werkzeug für Entwickler, die zukunftssichere und wartbare Hardware entwerfen möchten. Für Unternehmen und Entwicklungsteams, die neben Verlässlichkeit auch immer kürzere Time-to-Market-Zeiten realisieren möchten, bietet Veryl ein ideales Gleichgewicht zwischen Leistung und Benutzerfreundlichkeit. Es ermöglicht zudem eine schrittweise Migration und Integration in bestehende, auf SystemVerilog basierende Projekte, sodass das Risiko der Umstellung gering gehalten wird. Darüber hinaus erleichtern die umfangreichen Features wie integrierte Tests, automatische Formatierung, Echtzeit-Diagnosen und Dependency-Management den Arbeitsalltag deutlich.

Gerade in einer Zeit, in der Komplexität und Anforderungen stetig steigen, stellen solche Werkzeuge eine wichtige Hilfe dar, um nachhaltig hochwertige Hardwareprodukte zu entwickeln. Veryl belegt exemplarisch, wie die Weiterentwicklung von Hardware Description Languages nicht nur im Bereich der Technologie stattfinden kann, sondern durch eine kluge Kombination von Syntaxinnovationen, Developer Experience und Toolintegration signifikante Vorteile realisiert werden können. Wer nach einer modernen Alternative zu SystemVerilog sucht, profitiert von Veryl durch kürzere Entwicklungszeiten, bessere Übersichtlichkeit und eine zukunftsorientierte Ausrichtung des Hardwaredesigns.