In der heutigen Ära der digitalen Transformation sind effiziente Lösungen für komplexe kombinatorische Optimierungsprobleme essenziell. Diese Probleme, die unter anderem in Bereichen wie Schichtplanung, Verkehrsführung und Wirkstoffforschung auftreten, stellen aufgrund ihrer Komplexität eine enorme Herausforderung für traditionelle Computer dar. Sie benötigen oft unpraktisch lange Rechenzeiten, um eine optimale Lösung zu finden. Hier kommen spezialisierte Hardware-Systeme, sogenannte Annealing Prozessoren (APs), ins Spiel. Insbesondere der jüngste Fortschritt der sogenannten Dual Scalable Annealing Prozessoren (DSAPS) setzt einen Meilenstein in der Weiterentwicklung dieser Technologie und überwindet bislang bestehende Kapazitäts- sowie Präzisionsengpässe bei der Verarbeitung.

Annealing Prozessoren basieren auf dem Ising-Modell, einer physikalischen Methode zur Beschreibung von Systemen mit magnetischen Spins. Dabei repräsentieren Spins die Variablen der Optimierungsaufgabe, während Interaktionen zwischen den Spins die Nebenbedingungen und Zielkriterien darstellen. Ziel ist es, eine Spin-Konfiguration zu finden, die die Gesamtenergie des Systems minimiert, was einer optimalen oder zumindest sehr guten Lösung des Problems entspricht. Dies ermöglicht eine parallele und effiziente Verarbeitung, die bei klassischen Prozessoren kaum realisierbar ist. Das Ising-Modell teilt sich grundsätzlich in zwei Varianten: sparsely-coupled und fully-coupled Modelle.

Sparsely-coupled Modelle sind hoch skalierbar, da sie eine große Anzahl von Spins verarbeiten können, jedoch erfordern sie oft eine problematische Transformation der Optimierungsaufgaben, um diese passend abzubilden. Fully-coupled Modelle bieten dagegen eine deutlich flexiblere Abbildung nahezu aller kombinatorischer Probleme ohne umfangreiche Umformungen. Allerdings bestehen hier technische Limitationen: die Anzahl der Spins ist begrenzt und ebenso die Präzision, mit der die Interaktionswerte dargestellt werden können — typischerweise mit nur 4 bis 8 Bit. Forscher der Technischen Universität Tokio, Japan, haben nun unter der Leitung von Professor Takayuki Kawahara eine innovative Lösung entwickelt, die diese Limitierungen erheblich entschärft. Die Dual Scalable Annealing Processing System (DSAPS) Technologie erlaubt erstmals die gleichzeitige Skalierung der Anzahl der Spins und der Interaktionsbitbreite innerhalb derselben Hardwarestruktur.

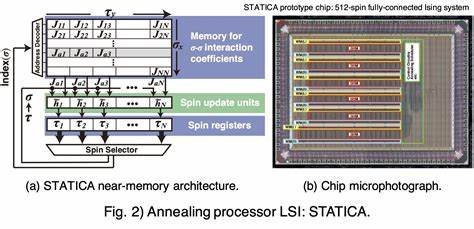

Dies ermöglicht nicht nur mehr Rechenkapazität, sondern auch eine höhere Genauigkeit bei der Darstellung und Berechnung der Wechselwirkungen im Ising-Modell. Kern der DSAPS-Technologie ist eine ausgeklügelte Manipulation sogenannter ∆E-Blöcke, die für die Energie-Berechnung des Systems zuständig sind. Diese werden in zwei unterschiedlichen Strukturen ausgeführt: einer herkömmlichen Struktur mit hoher Kapazität sowie einer neuartigen Struktur mit hoher Präzision. Ein ∆E-Block entspricht dabei im Hardware-Design einem großflächigen integrierten (LSI) Chip auf einer CMOS-basierten Annealing-Prozessor-Platine. Er enthält sowohl die Interaktionsmatrix als auch die Spins selbst.

Die hochkapazitive Struktur teilt jeden ∆E-Block in kleinere Subblöcke auf, die separat berechnet und anschließend durch eine zentrale Steuereinheit auf der Platine zusammengeführt werden. Dies führt zu einer einfachen und flexiblen Erhöhung der Spin-Anzahl, indem die Anzahl der Subblöcke einfach vergrößert wird. Die hochpräzise Struktur arbeitet hingegen mit mehreren ∆E-Blöcken, die gleiche Spin-Anzahlen und Interaktionen besitzen, jedoch auf unterschiedlichen Bit-Leveln berechnet werden. Die Steuerung fasst die Ergebnisse mittels Bitverschiebungen zusammen, was die effektive Interaktionsbitbreite vervielfacht. Ein praxisnahes Beispiel zeigt, dass mit vier ∆E-Blöcken auf unterschiedlichen Bitniveaus die Interaktionsbitbreite viermal so groß sein kann wie bei einem einzelnen Block.

Dies resultiert in einer vielfach höheren Präzision bei der Berechnung und ermöglicht das Lösen deutlich komplexerer und sensiblerer Optimierungsprobleme. Durch die steuernde Field Programmable Gate Array (FPGA)-Einheit können mehrere identische LSI-Chips koordiniert werden, um so ein skalierbares und flexibles System zu schaffen. Die Flexibilität des DSAPS ist bemerkenswert, da es sowohl für sparsely-coupled als auch fully-coupled Ising Modelle verwendet werden kann. Dies öffnet vielen Anwendungsfeldern den Weg zu maßgeschneiderten Lösungen mit hoher Rechenleistung und Genauigkeit. Die Forscher haben die Machbarkeit der Technologie mit zwei Konfigurationen auf einer CMOS-AP-Platine demonstriert: Ein System arbeitete mit 2048 Spins bei 10-Bit-Interaktionen und vier parallelen Threads, das andere mit 1024 Spins, 37-Bit-Interaktionen und zwei Threads.

Die Erhöhung der Interaktionsbitbreite auf bis zu 37 Bit ist ein großer Fortschritt im Vergleich zu bisherigen ASIC-basierten Lösungen, die meist lediglich 4 bis 8 Bit erreichen. Validierungstests auf dem MAX-CUT Problem zeigten eine beeindruckende Genauigkeit von über 99 % im Vergleich zu theoretisch besten Ergebnissen. Bei komplexeren Problemen, wie dem 0-1-Rucksackproblem, unterschied sich die Leistungsfähigkeit je nach Konfiguration merklich. Das System mit 10-Bit-Interaktionen zeigte eine erhebliche Abweichung von fast 99 %, während die 37-Bit-Variante eine sehr geringe durchschnittliche Abweichung von nur 0,73 % erreichte. Dies unterstreicht die Bedeutung, geeignete Systemkonfigurationen entsprechend der Aufgabencharakteristik zu wählen.

Die Innovationskraft des DSAPS Systems liegt nicht nur in der technischen Leistung, sondern auch in der breiten Anwendbarkeit. Mit der Fähigkeit, sowohl mehr Spins als auch eine höhere Präzision zu integrieren, können präzisere und effizientere Lösungen für praktische Probleme realisiert werden. Dies könnte weitreichende Auswirkungen auf die Planung logistischer Abläufe, Optimierungsalgorithmen in der Verkehrssteuerung, sowie die Entwicklung neuer Medikamente haben, deren molekulare Wechselwirkungen äußerst komplex sind und hoher Präzision bedürfen. Professor Kawahara hebt hervor, dass das DSAPS-System einen Wendepunkt in der Entwicklung skalierbarer APs markiert. Zudem wird das System ab 2025 in das Lehrprogramm für dritte Studienjahre integriert, um Studierenden praktische Erfahrungen und Einsichten im Bereich Halbleiter-Design und Ising-Maschinen zu vermitteln.

Dies fördert nicht nur die akademische Bildung, sondern beschleunigt auch den Transfer fortschrittlicher Technologien in die Industrie. Die zugrundeliegenden Förderungen durch die Japan Society for the Promotion of Science (JSPS) unterstreichen die bedeutende Stellung dieses Forschungsprojekts. In der Kombination aus grundlegender physikalischer Modellierung, state-of-the-art Halbleitertechnik und praxisorientiertem Anwendungsbezug setzt die DSAPS-Technologie neue Maßstäbe in der kontinuierlichen Verbesserung der Computerleistung außerhalb konventioneller Architekturen. Insgesamt eröffnet das Dual Scalable Annealing Processing System eine vielversprechende Perspektive für die Zukunft der combinatorialen Optimierung und der Ising-basierten Rechentechnologien. Die Fähigkeit zur gleichzeitigen Skalierung von Spin-Kapazität und Interaktionspräzision könnte in den kommenden Jahren eine Vielzahl von Branchen transformieren und als Schlüsseltechnologie für komplexe Problemlösungen gelten.

Abschließend lässt sich sagen, dass die Entwicklung des DSAPS-Systems einen bedeutsamen Schritt in Richtung einer neuen Generation von Annealing-Prozessoren darstellt, die den Anforderungen moderner Optimierungsaufgaben gewachsen sind. Mit der Kombination aus technischer Innovation und praktischer Einsetzbarkeit positioniert sich die Technologie als ein wichtiges Instrument für Wissenschaft und Industrie gleichermaßen.