Die rasante Entwicklung der Künstlichen Intelligenz (KI) und maschinellen Lernens erfordert leistungsfähige Hardware zur effizienten Verarbeitung komplexer neuronaler Netzwerke. Google hat mit der Einführung der Tensor Processing Unit (TPU) einen maßgeblichen Schritt in Richtung spezialisierter KI-Beschleuniger gemacht. Doch diese Technologie ist proprietär und für viele Entwickler und Forschungseinrichtungen nicht direkt zugänglich. OpenTPU setzt genau hier an, indem es eine quelloffene Nachbildung der TPU bereitstellt, die sowohl für Bildungszwecke als auch für die Weiterentwicklung von KI-Hardware neue Chancen eröffnet. OpenTPU ist ein Projekt des UC Santa Barbara ArchLab und basiert auf den verfügbaren Designinformationen von Googles TPU, insbesondere dem Forschungsbericht "In-Datacenter Performance Analysis of a Tensor Processing Unit".

Obwohl Google keine formalen Spezifikationen oder eine vollständige ISA (Instruction Set Architecture) veröffentlicht hat, ermöglicht OpenTPU durch sorgfältige Reverse-Engineering-Methoden und PyRTL-basierte Implementierung eine funktionale Repräsentation der TPU-Hardware. Die OpenTPU-Hardware konzentriert sich derzeit hauptsächlich auf die Beschleunigung der Inferenzphase neuronaler Netze, im Speziellen auf Operationen wie Matrixmultiplikationen, ReLU- und Sigmoid-Aktivierungen. Ein wesentlicher Vorteil von OpenTPU liegt in seiner Flexibilität: Die Hardware ist parametrisiert, insbesondere hinsichtlich der Größe des Matrixmultiplikationseinheitsarrays. So lässt sich die Größe der Systolischen Matrix-Multiplikations-Einheit leicht an den jeweiligen Anwendungsfall oder das Simulationsszenario anpassen. Durch den Einsatz von PyRTL, einer Python-basierten Hardwarebeschreibungssprache, ist das System nicht nur simulativ zugänglich, sondern kann zudem als Grundlage für die automatische Generierung von Verilog-Code dienen.

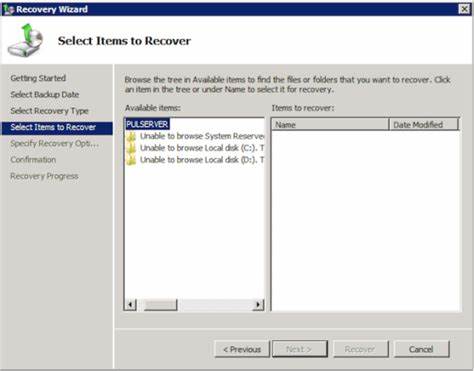

Dies gibt Entwicklern die Möglichkeit, die Schaltung in traditionelle Hardwarebeschreibungssprachen zu überführen und weiterzuentwickeln. Im Bereich der Softwareunterstützung bietet OpenTPU eine Reihe von Werkzeugen, die den Entwicklungszyklus erleichtern. So existieren Funktional- und Hardwaresimulatoren, die verschiedene Ausführungsmodi und Quantisierungsstufen abdecken. Die Simulatoren unterscheiden etwa zwischen 32-Bit-Fließkommazahlen und 8-Bit-Integerrechnungen, was die Analyse von Präzisions- und Leistungsaspekten erleichtert. Zur Verifikation bietet OpenTPU ein Checker-Tool, das die Übereinstimmung zwischen Softwareresultaten, Simulator-Ausgaben und Hardware-Simulation prüft, wodurch eine verlässliche Entwicklung gewährleistet wird.

OpenTPU unterstützt eine Auswahl zentraler Anweisungen, die für KI-Inferenzprozesse relevant sind. Dazu zählen beispielsweise das Lesen und Schreiben von Host-Speicher- und Gewichts-Daten, Matrixmultiplikationen mit verschiedenen Flags für Überschreibung oder Gewichtstausch sowie Aktivierungsfunktionen mit verschiedenen Modi. Die Ausführung erfolgt dabei deterministisch, wobei dynamische Speicherzugriffsverzögerungen theoretisch möglich sind, jedoch in der aktuellen Implementierung nicht modelliert werden. Das Fehlen einer „repeat“-Anweisung bedeutet zudem, dass NOPs (No Operation) häufig für Timing-Paddings eingesetzt werden müssen, was die Programmierung etwas umständlich gestaltet, jedoch die kontrollierte Steuerung über den Ablauf gewährleistet. Auf der mikroarchitektonischen Ebene zeichnet sich OpenTPU durch eine auf 8-Bit-Multiply-Accumulate-Einheiten basierende Matrix-Multiplikationsstruktur aus.

Jede solcher Einheiten verbindet Multiplikation mit anschließender Addition und verfügt über eine eigene Zwischenspeicherung von Gewichten in zwei Pufferbanken. Der systolische Aufbau sorgt dafür, dass Eingabedaten diagonal in die Matrix gespeist werden, wodurch eine effiziente Parallelverarbeitung und Datenflusssteuerung realisiert wird. Die Zwischenergebnisse werden in einem Satz von Akkumulator-Puffern vorgehalten, aus denen spätere Aktivierungen nach definierten Funktionen erfolgen. Gewichtsdaten werden aus einem vorgelagerten FIFO-Puffer gestaffelt durch die Einheiten geleitet, was Stalls durch Speicherverzögerungen vermeiden hilft. Das mögliche Anwendungsspektrum von OpenTPU ist breit gefächert, wobei derzeit vor allem die Bedienung typischer Matrixmultiplikations- und Aktivierungs-Workloads in neuronalen Netzen abgedeckt wird.

So können beispielsweise Regressionen auf Datensätzen wie dem Boston Housing Dataset simuliert und validiert werden, ebenso das Training und Ausführen einfacher zweischichtiger neuronaler Netze. Viele weitere Anwendungsfälle aus der Deep-Learning-Praxis, beispielsweise mit TensorFlow erstellte Modelle, sind kompatibel, sofern sie mit den vorhandenen Gewichtsmatrizen und Aktivierungen korrespondieren. Das Projekt erlaubt es darüber hinaus, Trainingsdaten und Gewichte in passender Form zu erzeugen, sowohl im 8-Bit-Integer- als auch im 32-Bit-Fließkommaustauschformat. Entwickler können so relativ einfach experimentelle Datensätze aufsetzen, trainierte Modelle generieren und diese dann direkt in der Hardware- oder Simulatorumgebung von OpenTPU evaluieren. Der iterative Workflow zwischen High-Level-Anwendung und Hardware-Beschleuniger wird dadurch nahtlos unterstützt.

OpenTPU adressiert auch mögliche Abstraktionen und Lücken im Vergleich zur kommerziellen TPU. Während wesentliche Komponenten wie das Matrix-Multiplikationselement, einheitlicher Zwischenspeicher (Unified Buffer), Aktivierungseinheit, Akkumulatoren und Gewichtspuffer abgebildet sind, fehlen komplexere Funktionen wie Convolution, Pooling oder programmierbare Normalisierung bislang. Ebenso sind einige erweiterte Instruktionen der TPU-Architektur in OpenTPU nicht implementiert, etwa Synchronisationsbefehle. Diese Defizite sind jedoch Teil des offenen Entwicklungsansatzes und könnten durch Beiträge der Community im Laufe der Zeit ergänzt werden. Die Open-Source-Natur von OpenTPU bedeutet nicht nur Zugang zum Quellcode, sondern auch eine Plattform für Kollaboration und Innovation.

Entwickler, Wissenschaftler und interessierte Unternehmen können die TPU-Architektur erforschen, Modifikationen ausprobieren und neue Hardwarekonzepte testen, ohne von proprietären Einschränkungen blockiert zu sein. Die Möglichkeit, den Hardwareentwurf direkt im Python-Ökosystem zu simulieren und zu entwickeln, beschleunigt diesen Prozess zudem erheblich. In puncto Effizienz und Performance ist OpenTPU im Alpha-Stadium, weshalb vollständige Synthese- und Taktfrequenzbenchmarks noch ausstehen. Die flexible Konfigurierbarkeit der Hardware erlaubt jedoch eine Anpassung auf verschiedene Einsatzbereiche und Skalierungsstufen, angefangen von kleinen 8x8-Matrixeinheiten bis hin zu einem vollständigen 256x256 System. Dies macht OpenTPU zu einem einzigartigen Werkzeug für Erforschung, Lehre und Prädiktion zukünftiger TPU-Designvarianten.

Das OpenTPU-Projekt ist eine Antwort auf die zunehmende Bedeutung spezialisierter Hardware für KI-Anwendungen und den Bedarf an transparente, offene Systeme zur Förderung von Innovation. Es erlaubt eine tiefgreifende Auseinandersetzung mit moderner KI-Beschleunigerarchitektur, unterstützt die Analyse von Laufzeitverhalten, Speichermanagement, Instruktionsdesign und Mikroarchitektur und liefert eine Grundlage für Weiterentwicklungen im Hardwarebereich. Die Kombination aus Python-basierter Entwicklung, offener Quellcode-Verfügbarkeit und umfassender Simulation macht OpenTPU zu einem attraktiven Werkzeug für Lehrende und Studierende im Bereich Hardware-Design, für Forscher, die Architekturstudien durchführen, und für Unternehmen mit Interesse an KI-Hardwareentwicklung. Durch die enge Anlehnung an Google TPU, obgleich ohne exakte Kompatibilität, ist das Projekt zudem ein Fenster in die Zukunft industrieller KI-Beschleunigertechnologien. Abschließend zeigt OpenTPU eindrucksvoll, wie Open-Source-Projekte den Zugang zu Hightech-Hardware demokratisieren können.

Es bietet die Möglichkeit, theoretisches Designwissen mit praxisnahen Simulationen zu verbinden, um so die Entwicklung komplexer KI-Systeme zu beschleunigen. Die kontinuierliche Weiterentwicklung und mögliche Erweiterungen des Projekts könnten langfristig einen bedeutenden Beitrag zur KI-Gemeinschaft leisten und neue Standards in der Hardwareentwicklung setzen.

![Testing the Hard Stuff and Staying Sane [video] (2014)](/images/E84026CE-9357-45F5-90CB-05EDE204E3A6)