In der heutigen digitalen Welt sind hochauflösende Bild- und Videoübertragungen zur Norm geworden. Insbesondere 4K-Auflösungen mit 60 Hertz sind in Fernsehern, Überwachungssystemen, professionellen Kameras und anderen Anwendungsbereichen weit verbreitet. Doch die Implementierung von 4K-Video in Echtzeit stellt hohe Anforderungen an die Hardware, insbesondere wenn niedrige Latenzen, hohe Bandbreiten und Robustheit gefordert sind. Hier kommen Field Programmable Gate Arrays, kurz FPGAs, ins Spiel. Diese programmierbaren integrierten Schaltkreise bieten Flexibilität und Leistung, um anspruchsvolle Bildverarbeitungsaufgaben zu bewältigen.

Ein aktuelles Beispiel ist die Nutzung des AMD Artix UltraScale+ FPGA auf der AUBoard-Plattform, mit der 4K-Bildverarbeitung bei 60 Hz über HDMI 2.0 realisiert wird. Das eröffnet neue Möglichkeiten für Entwickler und Unternehmen im Bereich Hochleistungsbildverarbeitung. FPGAs haben in den vergangenen Jahren einen enormen technischen Fortschritt erlebt. Sie bieten eine Kombination aus hoher Parallelität, Hardware-naher Verarbeitung und flexibler Anpassbarkeit.

Für die Verarbeitung von 4K-Videosignalen – was Datenraten von bis zu 18 Gigabit pro Sekunde bedeutet – ist genau diese Leistungsfähigkeit entscheidend. Nicht nur muss der Datenstrom in Echtzeit dekodiert, verarbeitet und neu kodiert werden, sondern auch spezifische Protokolle wie HDMI 2.0 müssen vollständig unterstützt werden. Die AUBoard-Lösung zeigt eindrucksvoll, wie der AMD Artix UltraScale+ FPGA mit seinen integrierten GTH-Transceivern diese Aufgabe übernimmt. Diese Transceiver sind spezialisierte Hochgeschwindigkeits-Schnittstellen, die Signale mit mehreren Gigabit pro Sekunde verarbeiten können, was sie ideal für HDMI 2.

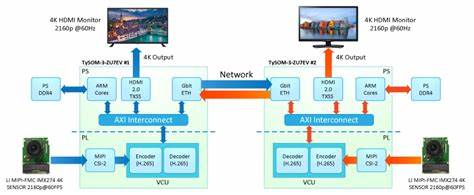

0 mit seinen vier TMDS-Datenlanes macht. Von grundlegender Bedeutung für das Projekt ist die Implementierung eines Referenzdesigns, das als Basis für Bildübertragung und -verarbeitung fungiert. Kernbestandteil dieses Designs ist das Zusammenspiel mehrerer Subsysteme. Das HDMI-RX-Subsystem empfängt das HDMI-Eingangssignal von Kamera oder Laptop und wandelt es in einen als Video-Stream nutzbaren Datenstrom um. Das HDMI-TX-Subsystem übernimmt die Aufgaben der Videoausgabe und wandelt den Video-Stream zurück in ein HDMI-Signal.

Zentrale Schnittstelle ist der sogenannte Video PHY Controller, der zwischen den Transceivern und den HDMI-Subsystemen vermittelt und dafür sorgt, dass die Daten korrekt synchronisiert und übertragen werden. Eine zusätzliche Besonderheit des Designs ist die Integration eines MicroBlaze-Prozessors, eines Soft-Core-Prozessors von AMD, der im FPGA implementiert ist. Dieser Controller ermöglicht die Konfiguration der IP-Blöcke innerhalb des Systems, steuert Menüs für die einfache Bedienung und programmiert die notwendigen Clock-Generatoren auf der AUBoard-Plattform. Ohne diesen intelligenten Steuermechanismus wäre eine flexible und nutzerfreundliche Bedienung des Systems kaum möglich. Gleichzeitig bietet er Raum für weitere Imaging-Algorithmen und -Filter, die sich nahtlos in die Pipeline integrieren lassen.

Ein weiterer interessanter Aspekt ist der Umgang mit Test- und Diagnosesignalen. Wenn keine Live-Videoquelle angeschlossen ist, kann das System über einen Testbildgenerator ein standardisiertes Bild ausgeben. Dies ist hilfreich für die Validierung der Hardware und die Fehlersuche, ohne dass ständig eine externe Kamera benötigt wird. Das System ist so aufgebaut, dass es Videodaten in verschiedenen Konfigurationen verarbeiten kann, etwa mit zwei oder vier Pixeln pro Taktzyklus. Diese Flexibilität ermöglicht je nach Anwendung die optimale Balance zwischen Ressourcenverbrauch und Leistung.

Grundlegend für die Funktionalität ist die Einbindung des HDMI 2.0-Standards. Während frühere Systeme oft nur HDMI 1.4 unterstützten und damit lediglich 4K-Auflösungen bei niedrigen Bildraten oder Full-HD mit sehr hohen Bildraten erlaubten, stellt HDMI 2.0 mit seinem hohen Datendurchsatz die Weichen für echte 4K-Übertragungen bei 60 Hz oder höher.

Die AUBoard ist aufgrund des speziell entwickelten Hardwaredesigns und der GTH-Transceiver hervorragend für diese Anforderungen geeignet. Mit zahlreichen I2C-Schnittstellen werden zudem die typischen HDMI-DDC-Kanäle (Display Data Channel) für Kommunikation mit Peripheriegeräten unterstützt. Diese gewährleisten, dass beispielsweise HDCP-Kopierschutz oder EDID-Informationsaustausch zuverlässig funktionieren. Die technische Umsetzung verändert auch den Entwicklungsprozess. Entwickler benötigen eine passende Toolchain für die FPGA-Konfiguration und Softwareentwicklung.

AMD stellt hierfür das Vivado Design Suite als Werkzeug für Hardware-Design und das Vitis Unified Software Platform für die Anwendungssoftware bereit. Über Generation und Lizenzeinbindung der HDMI-IP-Kerne wird ein reibungsloser Workflow für das Erstellen, Konfigurieren und Debuggen des Systems gewährleistet. Die Lizenzierung der HDMI-IP ist dabei essenziell und wird über den AMD License Manager abgewickelt. Ohne gültige Lizenz könnten die für die HDMI-Funktionalität notwendigen Module nicht erzeugt werden. Die neue Referenzdesign-Basis ermöglicht es, die ausgewählte Beispielimplementierung für die VCU118-Plattform anzupassen und auf die AUBoard zu übertragen.

Dabei sind einige wichtige Änderungen insbesondere in der Video-PHY-Komponente notwendig, um die Gegebenheiten der GTH-Transceiver des Ultrascale+-FPGAs zu berücksichtigen. Technische Details wie die Nutzung der PLL-Clock-Pipes sorgen für ein stabiles und sicheres Taktsignal, das für die Übertragung der hochauflösenden Videodaten zwingend erforderlich ist. Ein wesentliches Element ist auch die Anpassung der FPGA-Pinbelegung. Für die Anschlüsse des HDMI-Eingangs und -Ausgangs, der Clock-Signale, der I2C-Leitungen und der UART-Interface, die zur Steuerung und Diagnose genutzt werden, sind spezifische GPIO-Pins des FPGAs an das Board-Layout gebunden. Hier sorgt eine sorgfältig erstellte XDC-Datei (Constraints-File) für eine korrekte Verbindung zwischen der Hardwareseite und der FPGA-Logik.

Darüber hinaus spielen weitere Signale wie LED-Indikatoren für Betriebszustände oder Reset-Leitungen wichtige Rollen im Gesamtsystem. Von der Softwareseite betrachtet startet man mit der Erstellung einer einfachen „Hello World“-Anwendung auf dem MicroBlaze-Prozessor, um die Systemintegrität und Entwicklungsumgebung zu überprüfen. Danach wird mit dem v_hdmi_rx_ss-Treiber, der speziell für HDMI-Empfangs-Subsysteme vorgesehen ist, eine Anwendung zur Bilddurchschleusung („Passthrough“) eingerichtet. Dieser Ansatz gibt Entwicklern eine solide Grundlage, um nachfolgend komplexere Bildverarbeitungsroutinen oder Filter zu implementieren, ohne den Signalfluss zu unterbrechen. Ein interessanter, technischer Kniff liegt in der Anpassung der Ansteuerung des Taktgenerators.

Standardmäßig erwarten viele Softwarebeispiele eine Programmierung des Si5324-Taktgenerators per I2C. Die AUBoard nutzt jedoch einen Renesas 8T49N24-Chip, was bedeutet, dass die Software entsprechend angepasst werden muss. Diese Änderung ist in der Anwendung integriert und stellt sicher, dass der FPGA immer mit den korrekten Referenztakten versorgt wird und somit die hohen Datenraten bei HDMI 2.0 zuverlässig verarbeitet werden können. Die praktische Inbetriebnahme gestaltet sich vergleichsweise einfach.

Es genügt, eine HDMI-Quelle (etwa eine 4K-Kamera) und ein HDMI-Ausgabegerät (einen Monitor) mit der AUBoard zu verbinden. Ein spezieller DIP-Schalter am Board verwaltet den FPGA-Reset und sollte für den normalen Betrieb deaktiviert sein. Nach dem Hochfahren läuft die Software automatisch und das HDMI-Signal wird realzeitfähig durchgereicht. Über UART besteht zudem die Möglichkeit, eine einfache Steuerung zu aktivieren und Statusinformationen sowie Log-Meldungen auszulesen. Der große Vorteil dieser Lösung besteht neben der hochqualitativen Bildverarbeitung darin, dass das eigentliche FPGA-Design äußerst ressourcenschonend ausfällt.

Über 70 Prozent der FPGA-Ressourcen bleiben frei, um weitere Bildverarbeitungsalgorithmen, wie etwa Rauschfilter, Kantenerkennung oder Farbraumanpassungen, zu implementieren. Dies macht das Gesamtsystem außerordentlich flexibel, skalierbar und geeignet für den Einsatz in unterschiedlichsten sicheren und leistungsstarken Imaging-Anwendungen. Die Kombination aus leistungsfähiger Hardware, dem modularen Referenzdesign und der umfassenden Entwicklungsumgebung macht FPGAs wie den AMD Artix UltraScale+ zum optimalen Werkzeug für Entwicklerfirmen, Forschungsinstitute und Betreiber, die 4K-Video in Echtzeit übertragen, analysieren oder verarbeiten wollen. Dabei öffnet die offene Architektur allen Anwendern die Möglichkeit, individuelle Anpassungen vorzunehmen und so maßgeschneiderte Imaging-Lösungen zu realisieren, die exakt auf die jeweilige Anwendung zugeschnitten sind. In Zukunft sind weitere spannende Entwicklungen zu erwarten.

So könnten energieeffiziente Filter und KI-basierte Bildverarbeitungsmodule direkt in die Pipelines integriert werden. Die Übertragungsstandards entwickeln sich ebenfalls weiter, eventuell werden UHD-Standards jenseits von 4K bei noch höheren Frameraten für Ultrabreitbild- und XR-Anwendungen relevant. Die offene Plattform basierend auf FPGAs gibt hier den nötigen Freiraum für Innovationssprünge. Zusammengefasst steht die Nutzung von FPGAs als Herzstück für 4K-Bildverarbeitung heute für eine Kombination aus größtmöglicher Flexibilität, hoher Leistung und industrieller Reife. Die Demonstration daran, wie das AUBoard auf Basis eines AMD Artix UltraScale+ die HDMI 2.

0-Spezifikation mit 4K bei 60 Hz realisiert, verdeutlicht, dass hardwarebasierte Imaging-Systeme der nächste Schritt in der Videotechnologie sind. Entwickler können so mit weniger Aufwand robuste und leistungsfähige Lösungen schaffen, die sich perfekt in moderne Medienlandschaften einfügen und den Anforderungen künftiger Anwendungen gerecht werden.