Der Intel 386 Prozessor, eingeführt im Jahr 1985, markiert einen enorm wichtigen Meilenstein in der Entwicklung von Prozessoren. Er war der erste 32-Bit-Prozessor der x86 Architektur und ebnete den Weg für modernen Computerleistung. Zentrales Element seines Designs sind die Register, Speicherzellen, die eine sehr schnelle Datenverarbeitung ermöglichen und dadurch den Zugriff auf häufig benötigte Daten massiv beschleunigen. Die Umsetzung dieser Register im 386 ist jedoch kein einfaches Thema – im Gegenteil, die zugrundeliegende Schaltung ist viel komplexer und raffinierter, als man erwarten würde. Das Design folgt nicht dem üblichen Ansatz einer einheitlichen Registerstruktur, sondern benutzt sechs unterschiedliche Schaltungsarten, um den verschiedenen Anforderungen der Register gerecht zu werden und gleichzeitig die Leistung zu maximieren.

Die Register des 386 sind in mehrere Kategorien eingeteilt. Es gibt die sogenannten General-Purpose Register (Allzweckregister), Indexregister für Adressberechnungen, Segmentregister zur Speicherverwaltung sowie spezielle Register für Statusinformationen und Betriebssystemfunktionen. Insgesamt gibt es etwa 16 der für Programmierer sichtbaren Register, doch auf dem Chip befinden sich noch viele weitere temporäre und systeminterne Register, die von der Mikroprogrammsteuerung beziehungsweise spezielleren Einheiten genutzt werden. Ein grundlegendes Bauelement bei der Umsetzung der Register ist die Verwendung von sogenannten statischen RAM-Zellen. Diese speichern jeweils ein Bit über eine sogenannte Inverter-Schleife, die sich im stabilen Zustand entweder im Zustand 0 oder 1 befinden kann.

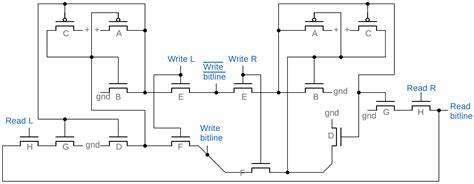

Ein solcher statischer Speicherelement-Typ ist schneller und zuverlässiger als dynamischer RAM, der für Hauptspeicher verwendet wird, jedoch auch etwas größer und transistorintensiver. Im 386 ist die Registerstruktur daher mit statischen RAM-Zellen realisiert, um die hohen Geschwindigkeitsanforderungen zu erfüllen. Die klassischen statischen Speicherelemente verfügen über sechs Transistoren, weshalb sie als 6T-Zellen bezeichnet werden. Dabei sorgen zwei rückgekoppelte Inverter dafür, dass ein Bit stabil gespeichert wird. Über sogenannte Pass-Transistoren wird dann das Lesen und Schreiben von Daten ermöglicht.

Die einfache 6T-Zelle kann gleichzeitig jedoch nur lesen oder schreiben, was für Register unpraktisch ist, da mehrere Register oft gleichzeitig gelesen werden müssen, während gleichzeitig in ein Register geschrieben wird. Aus diesem Grund entwickelte Intel für den 386 eine Weiterentwicklung der Speicherelemente mit acht Transistoren, die 8T-Zellen genannt werden. Diese erlauben eine sogenannte doppelte Portierung, also das gleichzeitige Lesen von zwei Registern parallel zum Schreiben in ein drittes. Dies ist eine Kernanforderung für die Prozessor-Performance, da Rechenoperationen oft zwei Operanden aus Registern lesen und das Ergebnis in einem dritten Register speichern. Hierdurch wird die interne Datenverarbeitung ohne Verzögerungen möglich.

Die Register selbst sind im Silizium-Chip in einem hochstrukturierten Raster angeordnet. Jede Registerzelle bildet eine horizontale Bahn im Chip-Design, in dem jede der 32 Bits des Registers exakt 60 Mikrometer breit ist und sich so gleichmäßig aneinanderfügen lässt. Die Datenbusse verlaufen vertikal, so dass Informationen in Form von 32-Bit-Wörtern zwischen den Registern und der Recheneinheit hin- und herfließen. Steuerleitungen verlaufen horizontal und aktivieren die richtigen Register zum Lesen oder Schreiben, abhängig von der gerade ausgeführten Prozessoranweisung. Eine bemerkenswerte Eigenheit des 386 Registerdesigns ist die Verwendung von sechs verschiedenen Schaltungstypen, um die 30 auf dem Chip implementierten Register abzubilden.

So gibt es beispielsweise Register, die nur 16 Bits breit sind und mit doppelt dicht gepackten 8T-Zellen realisiert wurden. Andere 32-Bit-Register können bis zu drei Ports unterstützen, was bedeutet, dass in einem Zyklus gleichzeitig zwei Register gelesen und ein drittes beschrieben werden kann. Einige Register können sogar flexible Zugriffslängen unterstützen: bestimmte Bytes innerhalb eines Registers lassen sich separat adressieren und schreiben. Das war eine direkte Folge der Kompatibilitätsanforderungen mit der älteren x86 Architektur, bei der 32-Bit-Register in mehrere Teilbereiche wie 16-Bit- und 8-Bit-Register unterteilt sind. Die legendären Allzweckregister EAX, EBX, ECX und EDX zum Beispiel unterstützen aufgrund der x86 Historie auch Zugriff auf ihre jeweils unteren 16 Bit als 16-Bit-Register AX, BX, CX, DX sowie auf die unteren und oberen Bytes als AL, AH, BL, BH und so weiter.

Dies erfordert komplexe Steuerleitungen, die selektives Schreiben von 8-Bit-Teilen innerhalb eines 32-Bit-Registers erlauben. Eine einfache rechteindeutige Linearisierung der Bits reicht hier nicht aus, da innerhalb des Registerchips Bits physikalisch anders angeordnet und verschränkt gespeichert werden. Tatsächlich liegen die unteren 16 Bits dieser Register in einer interleaved Struktur vor. Die unteren beiden Bytes sind so im Speicher verteilt, dass beispielsweise das niedrigstwertige Byte (AL) und das höherwertige Byte (AH) physisch nebeneinander liegen. Dies wird als Shuffle-Netzwerk bezeichnet und ist entscheidend für die effiziente Umsetzung der kleineren Registerzugriffe.

Dadurch kann eine 8-Bit-Berechnung im ALU ganz ohne aufwendige Verschiebungslogik durchgeführt werden, da die Bits schon passend verteilt sind. Beim Lesen und Schreiben durchlaufen Daten dieses Shuffle-Netzwerk und werden somit beim Zugriff gegeneinander getauscht oder in die richtige Reihenfolge gebracht. Neben den Allzweckregistern existieren weitere Register mit anderen Zugriffsmustern. So unterstützen die Register für den Stapelzeiger ESP, Basiszeiger EBP sowie die Indexregister ESI und EDI grundsätzlich 32-Bit- und 16-Bit-Zugriffe, aber keine 8-Bit-Teilschreibungen. Ihre Registerzellen sind entsprechend mit etwas einfacheren, jedoch ebenfalls hochoptimierten 10T-Zellen aufgebaut, die eine Doppel-Portierung erlauben, jedoch nicht die 8-Bit-Schreibmodi.

Die unteren 16-Bit-Register, welche beispielsweise die Segmentregister abbilden, werden – wie erwähnt – mit denselben 8T-Zellen gefertigt wie andere 16-Bit-Register, jedoch sind diese Zellen dichter gepackt, und es werden pro Bit zwei Registerzellen eng nebeneinander gebaut, sodass Register mit kleineren Bitbreiten sehr effizient realisiert sind. Die höchste Komplexität entfaltet sich bei einigen Spezialregistern, die intern sogar die Möglichkeit bieten, Werte direkt von einem Register in ein anderem zu kopieren, ohne den Umweg über den Lese- und Schreibbus zu nehmen. Eine erste Registerkategorie verfügt daher über eine zusätzliche Kontrollleitung zum direkten Kopieren vom darunter liegenden Register, was sich vor allem bei bestimmten Systemoperationen als leistungsfördernd erweist. Diese Registerzellen sind auch in ihrer Transistorkonfiguration am aufwendigsten ausgeführt und nehmen messenmäßig die größte vertikale Fläche im Chip ein. Beeindruckend ist auch die äußerst sparsame und gleichzeitig leistungsorientierte Gestaltung der gesamten Registereinheit.

Jedes einzelne Bitregister ist exakt 60 Mikrometer breit – exakt gleich breit wie die Recheneinheiten und andere funktionale Schaltkreise, sodass die verschiedenen Bausteine im Chip wie Bausteine eines Legosystems aufeinanderstoßen und so eine möglichst kompakte Standardbauweise erreicht wird. Metallleitungen verlaufen vertikal durch die Registerbereiche, um Bits auf den Buslinien hin- und herzuschieben, während Steuerleitungen horizontal sitzen, womit ein durchdachtes zweidimensionales Steuer- und Datenübertragungssystem entsteht. Die verschiedenen Zelltypen verlangen unterschiedliche Steuerungsspannungen und verschiedene Wortleitungen. Diese steuern, welche Register zur gleichen Zeit gelesen oder beschrieben werden. Besonders raffiniert ist die Tatsache, dass viele Register drei verschiedene Wortleitungen für das Schreiben besitzen, womit Teile der Register separat beschrieben werden können – für das 8-Bit-Halbbyte, das 16-Bit-Halbregister oder das volle 32-Bit-Wort.

Daraus ergibt sich eine enorme Flexibilität, die notwendig ist, um die vielfältigen Anweisungen der x86-Befehlssätze zu unterstützen. Das technische Meisterwerk des Intel 386 ist nicht nur seine Prozessorleistung, sondern auch diese ausgeklügelte Registerstruktur, die Flexibilität, Geschwindigkeit und die weitreichende Kompatibilität zu Vorgängerprozessoren miteinander verbindet. Die Register sind nicht einfach nur „speichereinheiten“, sondern ein komplexer Mix an Speicherzellen, Hardware-Logik und Datenverschiebungseinheiten, jeder Teil maßgeschneidert für einen bestimmten Registertyp und seine Anforderungen. Durch diesen differenzierten Ansatz konnte Intel trotz eines konservativen Designs und der großen Kompatibilitätsverpflichtungen ein System erstellen, das selbst nach heutigen Maßstäben Eindruck macht. Es verdeutlicht auf beeindruckende Weise die Kluft zwischen theoretischem Schaltungsdesign und der tatsächlichen, praktischen Umsetzung in einem High-Performance-Mikroprozessor.

Zusätzlich macht der detaillierte Blick auf den 386 Registeraufbau auch verständlich, warum der x86-Prozessor eine derart komplexe Architektur besitzt – das sogenannte „Fluch der Rückwärtskompatibilität“, bei der jahrzehntelange alte Architekturentscheidungen bis heute moderne Prozessordesigns stark beeinflussen. Wäre modernes Design von Grund auf neu entwickelt worden, wäre vermutlich vieles deutlich einfacher und effizienter umsetzbar gewesen. Doch gerade diese Komplexität zeigt die Ingenieurskunst, mit der Intel die Balance zwischen Altem und Neuem gelungen ist. Zusammenfassend lässt sich sagen, dass die Registereinheiten des Intel 386 ein faszinierendes Beispiel für ausgefeilte Halbleitertechnik darstellen. Mit sechs unterschiedlichen Zellschaltungsarten, einem Shuffle-Netzwerk für 8- und 16-Bit-Zugriffe und der cleveren Verknüpfung der Register untereinander setzt der 386 Standards, die für seine Zeit revolutionär waren.

Die Einsicht in diese Registerarchitektur gibt auch heute noch wichtige Hinweise darauf, wie man die Balance zwischen Vielseitigkeit, Geschwindigkeit und Fertigung auf kleinstem Raum optimal gestaltet – Herausforderungen, denen sich jeder Chipentwickler seither immer wieder stellen muss.

![Stargate Data Center being built in Abilene, Texas [video]](/images/FA009368-EC5D-48C3-BCAC-AF0B85F4678C)