Vor 15 Jahren begann an der Universität von Kalifornien, Berkeley, eine Bewegung, die die Computertechnik grundlegend verändern sollte. RISC-V, eine offen lizenzierte Befehlssatzarchitektur (Instruction Set Architecture, ISA), startete als mutiges Graduiertenprojekt – heute ist sie eine der innovativsten und am schnellsten wachsenden Architekturen weltweit. Die Entwicklung von RISC-V ist ein Paradebeispiel dafür, wie hohe Risiken zu noch größeren Belohnungen führen können, von akademischer Forschung bis hin zu kommerziellen Anwendungen und sogar souveränen staatlichen Technologien. Die Ursprünge von RISC-V gehen auf das Frühjahr 2010 zurück, als der Student Andrew Waterman an der UC Berkeley erkannte, dass eine bereits bestehende, veraltete Architektur nicht den Anforderungen eines modernen Projekts gerecht werden konnte. Das Team um Professor Krste Asanović entschied sich gegen eine Revival der DEC Alpha, aufgrund deren architektonischer Einschränkungen und Altlasten.

Stattdessen wagten sie den Schritt, eine komplett neue, schlanke und offene Architektur zu entwickeln, die leicht erweiterbar und anpassbar ist. Die Entscheidung für Offenheit erwies sich als visionär, denn sie schuf eine Plattform, die nicht nur akademischen Zwecken diente, sondern weltweit eine neue Ära der Prozessorentwicklung einläutete. Die Offenheit von RISC-V ist eine der fundamentalen Triebfedern für dessen Erfolg. Als lizenzfreie und quelloffene ISA erlaubt RISC-V es Entwicklern, Unternehmen und Institutionen, maßgeschneiderte Prozessoren zu entwerfen und zu implementieren, ohne Kommunikationshürden durch Patente oder restriktive Lizenzgebühren. Anders als etablierte, proprietäre ISAs wie x86 oder ARM, deren Nutzung mit hohen Kosten und Einschränkungen verbunden ist, bietet RISC-V die Freiheit, Innovationen schneller und kostengünstiger umzusetzen.

In den Anfangsjahren war RISC-V vor allem in den Hörsälen und Forschungslabors präsent. Die akademische Gemeinschaft nahm das neue ISA-Konzept zunächst mit Skepsis auf, da konventionelle Curricula ihre geplanten Inhalte und Industrieanbindungen bevorzugten. Doch die technische Eleganz, die Modularität und vor allem der offene Charakter zogen langsam exklusives Interesse von außen auf sich. Die erste Veröffentlichung des RISC-V-Befehlshandbuchs im Mai 2011 markierte den Beginn eines breiteren Zugangs, wenngleich die Vision, die Architektur praktisch einzusetzen und zu verbreiten, noch viele Herausforderungen parat hielt. Der Wendepunkt folgte auf der Hot Chips Konferenz 2014, als Industrievertreter auf RISC-V aufmerksam wurden und die Vorteile einer offenen, flexiblen Architektur zunehmend erkannten.

Besonders Startups und Unternehmen, die schnelle Markteintritte anstrebten, sahen RISC-V als Möglichkeit, zeitaufwändige und teure Lizenzverhandlungen zu umgehen. Innovation konnte beschleunigt werden: von der Entwicklungszeit bis zur Markteinführung. Die Flexibilität, einen Kern spezifisch an eigene Bedürfnisse anzupassen, war oftmals wichtiger als allein Kostenvorteile. In der Folge stieg die Anzahl der Unternehmen, die Projekte auf Basis von RISC-V realisierten, rapide an. Große Technologiefirmen wie NVIDIA kündigten an, interne Komponenten auf RISC-V-Basis zu setzen, was die Vielseitigkeit und Zuverlässigkeit der Architektur unterstrich.

Ebenso integrierten Firmen wie Western Digital den RISC-V-Kern in ihre Produkte mit dem Ziel, jährlich Milliarden solcher Kerne auszuliefern – ein massiver Vertrauensbeweis für die grundsätzliche Reife und Stabilität des ISA. Mit wachsender kommerzieller Reife fand auch in der akademischen Welt ein Umdenken statt. Zwar hatten Universitäten anfänglich gezögert, doch die globale Industrieanforderung nach RISC-V-Kenntnissen führte bald zu einer Integration in Vorlesungen und Labore an renommierten Hochschulen wie MIT, ETH Zürich und anderen. Was einst ein Projekt zwischen ein paar Forschern war, wurde zum Standardwerkzeug für die nächste Generation von Computerarchitekten. Neben der technischen und didaktischen Bedeutung von RISC-V zeichnet sich ein weiterer Trend ab: Der Einfluss auf die nationale digitale Souveränität und Sicherheit.

Länder wie Indien, Brasilien und China haben RISC-V früh als strategisches Instrument erkannt, um weniger abhängig von internationalen Anbietern und deren proprietärer Hardware zu sein. Die Nutzung offener Standards erlaubt es, Entwicklungszyklen zu kontrollieren, Sicherheitsmaßnahmen maßgeschneidert umzusetzen und potenzielle Risiken durch fremdgesteuerte Abhängigkeiten zu minimieren. RISC-V hat sich zudem als Grundlage für spezialisierte Anwendungen bewährt, die klassische ISAs nur schwer oder mit hohen Kompromissen unterstützen können. Beispielhaft sind hier die Bereiche künstliche Intelligenz und maschinelles Lernen, in denen spezielle Vektor- und Matrixerweiterungen eine zentrale Rolle spielen. Die modulare Basisstruktur von RISC-V erlaubt die Einbindung solcher Erweiterungen gezielt und effizient, was besonders bei energieeffizienten Edge-Geräten und Leistungscomputern wertvolle Vorteile bringt.

In der Automobilindustrie entstehen dank RISC-V zukunftsfähige Mikrocontroller, die die Ansprüche moderner Software-definierter Fahrzeuge erfüllen. Die Möglichkeit, einen offenen, anpassbaren Kern mit sicheren und zuverlässigen Schnittstellen zu kombinieren, bringt dort enorme Erleichterungen für Hersteller und Entwickler. Der traditionelle Innovationszyklus im Automobil, der oft Jahre umfasste, wird so entscheidend beschleunigt, was in Zeiten der Elektrifizierung und Digitalisierung essenziell ist. Außerhalb der Erde etabliert sich RISC-V zunehmend als verlässliche Architektur für Weltraummissionen. Ihre Offenheit erlaubt Anpassungen für Widerstandsfähigkeit gegenüber Strahlung und Fehlerkorrekturmechanismen, die für Langzeitmissionen unabdingbar sind.

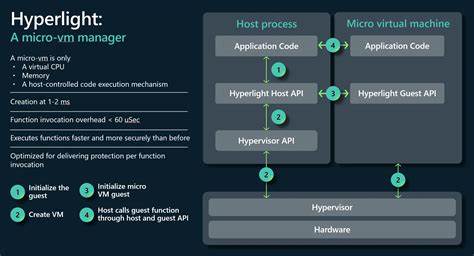

Erste erfolgreiche Einsätze auf der Internationalen Raumstation ISS und geplante SoCs mit RISC-V-Kernen für den Mond und Mars zeigen eindrucksvoll, wie weit die Technologie mittlerweile gereift ist. Die Entwicklung der Softwareumgebung bleibt für RISC-V eine vorrangige Herausforderung. Die Industrie arbeitet intensiv daran, robuste Toolchains, Betriebssystemunterstützung und Virtualisierungslösungen bereitzustellen, die die breite Marktdurchdringung erst möglich machen. Projekte wie die RISC-V Software Ecosystem Initiative (RISE) aggregieren die Kräfte großer Unternehmen und Open-Source-Communities, um diesen Prozess zu beschleunigen und die Akzeptanz zu erhöhen. Anwender wie der europäische Chip-Hersteller Codasip oder die OpenHW Group unterstützen durch verifizierte IP-Cores und offene Hardware-Projekte die Stabilisierung und Qualität in der RISC-V-Landschaft.

Dies bildet die Grundlage dafür, dass Sie als zukünftiger Entwickler oder Unternehmen auf ein bewährtes und dynamisch wachsendes Ökosystem zurückgreifen können. Der Blick in die Zukunft zeigt, dass RISC-V die Chance hat, sich als DAS offene ISA in nahezu allen Branchen und Technologieleveln zu etablieren. Die Kombination aus Flexibilität, Offenheit, Anpassbarkeit und einer engagierten Gemeinschaft bildet das Fundament für eine andauernde Innovationswelle – sowohl in der Forschung als auch in der industriellen Fertigung. Die Erfolgsgeschichte von RISC-V ist zugleich eine Kulturgeschichte: Ein globales Netzwerk von Entwicklern, Universitäten und Firmen arbeitet zusammen an der Weiterentwicklung, Standards und Tools. Diese kollektive Intelligenz verleiht RISC-V die Kraft, auch zukünftige Herausforderungen in Bereichen wie Sicherheit, Datenschutz, High Performance Computing und künstlicher Intelligenz zu bewältigen.

RISC-V ist mehr als nur eine technische Spezifikation – es ist ein offenes Forum des Fortschritts, die Antwort auf das Bedürfnis nach Transparenz und Innovation in einer zunehmend digitalisierten Welt. Die nächsten 15 Jahre versprechen eine spannende Reise, in der RISC-V die Basis für Computertechnik sein wird, die flexibel, risikoarm und gleichzeitig innovativ und nachhaltig gestaltet wird. Die Risiken, welche die Gründer einst eingingen, haben sich vielfach bezahlt gemacht – die digitale Zukunft könnte kaum vielversprechender aussehen.