Die stetig wachsende Komplexität moderner Mikroarchitekturen stellt Softwareentwickler vor große Herausforderungen, wenn es darum geht, die Leistung ihrer Anwendungen zu optimieren. Klassische Methoden zur Performance-Analyse stoßen oft an ihre Grenzen, weil sie eine überwältigende Datenflut generieren, die kaum aussagekräftig eingeordnet werden kann. Die sogenannte Top-Down Methodik setzt genau hier an, indem sie den Blick zunächst auf die Gesamtleistung richtet und anschließend schrittweise die Ursachen für mögliche Engpässe untersucht. Dies ermöglicht es, nicht nur offensichtliche, sondern auch feingranulare Performance-Probleme in superskalaren Out-of-Order-Prozessoren aufzudecken und gezielt zu beheben. Dabei spielt die Architektur der Performance Monitoring Units (PMUs) eine zentrale Rolle, da sie als Instrumente zur Erfassung relevanter Prozessorereignisse fungieren und die Grundlage für die Analyse bilden.

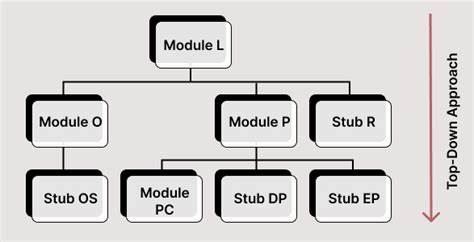

Eine der wesentlichen Herausforderungen in der Performance-Analyse besteht darin, aus hunderten möglicherweise erfassten Performance-Events jene auszuwählen, die tatsächlich als Flaschenhals auftreten. Historisch wurden PMUs oftmals in einer Bottom-Up-Manier entwickelt, bei der sogenannte „Dedicated Miss Events“ vordefiniert und Muster von häufig auftretenden Performance-Problemen abgebildet wurden. Diese Herangehensweise erweist sich jedoch als unzureichend für die immer vielfältiger werdenden Workloads und dynamischen Laufzeitverhältnisse moderner Systeme. Zudem können so nur Probleme erfasst werden, die bereits bei der Hardware-Entwicklung bekannt und antizipiert wurden. Im Gegensatz dazu verfolgt die Top-Down Methodik einen systematischeren, hierarchischen Ansatz, der von der obersten Leistungsebene ausgeht und einzelne Komponenten der Pipeline daraufhin untersucht, wie sie zum Performanceverlust beitragen.

Im Kern beschäftigt sich die Top-Down Analyse mit der Frage, wie die verfügbaren Prozessorressourcen genutzt oder blockiert werden. Sie gliedert die zur Untersuchung herangezogenen Metriken so, dass Entwickler auf einen Blick erkennen, ob der Prozessor zum Beispiel durch Front-End-Stalls, Back-End-Stalls, Retire-Stalls oder andere Faktoren ausgebremst wird. Jeder dieser Hauptfaktoren wird anschließend weiter und differenzierter betrachtet, um präzise Ursachen zu identifizieren. So wird aus einer zunächst abstrakten Performance-Datenmasse eine nachvollziehbare und handhabbare Informationsstruktur erzeugt. Das Resultat ist eine schnelle und effektive Ermittlung von Bottlenecks, die direkt in die Optimierungsarbeit einfließen kann.

Die Weiterentwicklung der PMU-Architektur trägt maßgeblich zum Erfolg der Top-Down Methodik bei. Im Vergleich zu älteren Systemen ist ein neues Set an Performance-Events implementiert worden, das mit minimalem Mehraufwand in bestehende Hardware integriert werden kann. Gerade einmal acht neue Events genügen, um eine umfassende Analyse zu ermöglichen. Diese Events erfassen feingranulare Daten über das Verhalten der Pipeline und erlauben eine differenzierte Betrachtung unterschiedlichster Engpässe. Bemerkenswert ist, dass diese Methode bereits in produktiven Prozessoren eingesetzt wird, was ihre Praxistauglichkeit und Effektivität unterstreicht.

Der Prozess der Performance-Analyse mit der Top-Down Methodik beginnt mit der Messung der Gesamtzeit, in der Anweisungen ausgeführt werden, den sogenannten Instruktionen pro Takt (IPC). Eine niedrige IPC-Rate signalisiert oftmals einen Engpass. Anschließend wird untersucht, welche Pipeline-Sektionen für diese schlechte Auslastung verantwortlich sind. So kann festgestellt werden, ob Probleme im Front-End liegen, beispielsweise durch langsames Laden von Instruktionen oder unterschiedliche Verzögerungen bei der Decodierung. Alternativ können Back-End-Bottlenecks den Datendurchsatz der Ausführungseinheiten limitieren oder Wartezeiten bei der Speicheranbindung auslösen.

Wird der Flaschenhals genauer definiert, kann gezielt auf höhere Optimierungen wie Code-Reorganisation, Anpassung der Speicherzugriffe oder Parallelisierung hingearbeitet werden. Besonders leistungsfähige, superskalare Prozessoren mit Out-of-Order-Ausführung erfordern eine noch genauere Betrachtung, da hier unterschiedliche Anweisungen unabhängig voneinander bearbeitet werden können, jedoch synchronisiert werden müssen. Die Top-Down Methodik erkennt subtile Verzögerungen, die etwa durch falsche Vorausberechnungen oder ineffiziente Nutzung von Reorder-Buffern entstehen. Diese Details gehen in anderen Analysemethoden oft verloren. Entwickler gewinnen hierdurch ein tiefes Verständnis für das Zusammenspiel von Hardware und Software auf Mikroarchitekturebene.

Für Softwareentwickler, die Anwendungen mit hohen Leistungsanforderungen entwickeln, schafft die Top-Down Methodik eine bislang kaum erreichbare Transparenz über den Zustand ihrer Programme während der Ausführung. Nicht nur kann man besser identifizieren, wo Rechenzeit verloren geht, sondern auch, wie sich Verarbeitungsengpässe vermeiden lassen. Das Ergebnis sind maßgeschneiderte Optimierungen auf Codeebene, die sich signifikant auf die Gesamteffizienz und Reaktionsfähigkeit des Systems auswirken. Insgesamt stellt die Top-Down Methodik einen Paradigmenwechsel in der Performance-Analyse dar. Sie ersetzt die oft fehleranfällige Bottom-Up-Analyse durch einen umfassenden systematischen Ansatz, der mit geringem Aufwand tiefgehende und differenzierte Einblicke in das Laufzeitverhalten von CPU-Code bietet.

Dank dieser Methode können Unternehmen und Entwickler leistungsfähigere Software erstellen, die auf modernen Prozessoren optimal skaliert und Ressourcen effizient nutzt. Damit leistet die Top-Down Analyse einen wichtigen Beitrag zur Bewältigung der stetig wachsenden Anforderungen an Computerleistung in Bereichen von Cloud-Computing über hochperformante wissenschaftliche Berechnungen bis hin zu Echtzeitanwendungen. Die fortschreitende Entwicklung und Integration solcher innovativen Analysetechniken in den Entwicklungsprozess wird auch weiterhin die Softwareoptimierung revolutionieren. Indem Bottlenecks präzise und schnell identifiziert werden, verringert sich der Zeitaufwand für Iterationen, Code kann zielgenau verbessert und letztlich die Benutzererfahrung spürbar gesteigert werden. Anwender profitieren von stabileren, reaktionsschnelleren Programmen, Entwickler von einer sichereren und effizienteren Entwicklungsumgebung.

So schließt sich der Kreis zwischen Hardware-Innovation und softwareseitiger Umsetzung. Für alle, die tiefere technische Einblicke in die Top-Down Methodik wünschen, empfiehlt es sich, die Entwicklung der Performance-Counters und konkrete Anwendungsszenarien in moderner Mikroarchitektur zu studieren. Zahlreiche Veröffentlichungen und Forschungsarbeiten, vor allem aus Fachkonferenzen und technischen Fachportalen, bieten umfangreiche Erläuterungen und Anwendungsbeispiele. Wer hier investiert, macht heute den entscheidenden Schritt, um den Herausforderungen der CPU-Performance-Optimierung in einer immer komplexer werdenden Hard- und Softwarewelt erfolgreich zu begegnen.