Die technologische Weiterentwicklung von Prozessorarchitekturen ist ein zentraler Treiber für Innovationen im Bereich der Computertechnik. Besonders in den letzten Jahren hat sich die offene RISC-V-Architektur als vielversprechende Alternative zu proprietären Designs etabliert. Vor diesem Hintergrund markiert die kürzliche Integration der Prozessordefinition für XiangShan-KunMingHu-V2R2 in den LLVM-Compiler ein bedeutendes Ereignis für Entwickler, Unternehmen und die gesamte Open-Source-Community. LLVM ist eine modulare Compiler-Infrastruktur, die weltweit von Softwareentwicklern genutzt wird, um effizienten und flexiblen Code für eine Vielzahl von Hardwareplattformen zu erzeugen. Durch die Aufnahme der XiangShan-KunMingHu-V2R2 Prozessordefinition erweitert LLVM die native Unterstützung für eine der modernsten RISC-V-Prozessoren, die vom Beijing Institute of Open Source Chip (BOSC) entwickelt wurde.

XiangShan-KunMingHu ist die dritte Generation eines hochleistungsfähigen, quelloffenen RISC-V-Prozessors mit Fokus auf Skalierbarkeit, Leistung und Erweiterbarkeit. Die XiangShan-KunMingHu-V2R2 Version stellt eine vollständig ausgereifte Iteration des Designs dar, das bereits in der Entwicklergemeinschaft für seine innovative Architektur und sein hohes Leistungspotential geschätzt wird. Das Projekt wird vom XSCC-Team im Rahmen der OpenXiangShan-Initiative gepflegt, welche darauf abzielt, Open-Source-Prozessorentwicklung voranzutreiben und zugänglich zu machen. Durch die Integration dieser Prozessordefinition in LLVM können Entwickler nun leichter optimierten Code generieren, der speziell auf die Eigenschaften und Instruktionssatz-Erweiterungen von XiangShan-KunMingHu abgestimmt ist. Die Bedeutung dieser Integration erstreckt sich weit über die reine Compiler-Technologie hinaus.

Sie signalisiert, dass die Entwicklung offener Hardwarearchitekturen zunehmend in professionelle Toolchains eingebunden wird, was einen wichtigen Schritt zur breiteren Akzeptanz und Nutzung offener Prozessorlösungen darstellt. Insbesondere Unternehmen, die auf RISC-V setzen, profitieren davon, da sie nun von besseren Optimierungsmöglichkeiten und umfassender Unterstützung bei der Erstellung von Software profitieren. XiangShan-KunMingHu unterscheidet sich durch eine Reihe anspruchsvoller ISA-Erweiterungen und Funktionalitäten, die eine erstklassige Ausführung von modernen Workloads gewährleisten. Das Design beinhaltet dynamische Ausführungsmöglichkeiten, verbesserte Speicherzugriffe sowie diverse spezielle Erweiterungen, die für moderne Anwendungsfälle wie künstliche Intelligenz und High-Performance-Computing optimiert sind. Die V2R2 Version ist aktuell stabil und gilt als eingefrorene Version, was bedeutet, dass darunter keine wesentlichen ISA-Veränderungen oder Pipelineänderungen mehr vorgenommen werden – ein entscheidender Faktor für die Stabilität in der Compilerunterstützung.

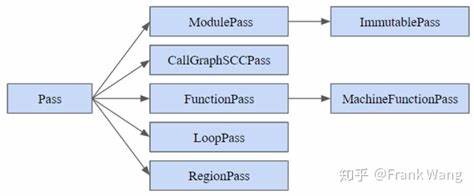

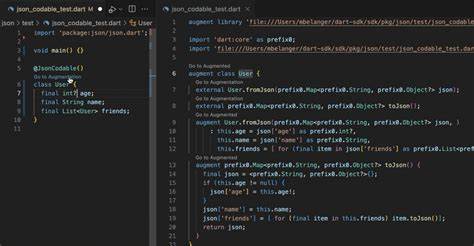

Eine der Herausforderungen bei der Arbeit mit komplexen Prozessorarchitekturen besteht darin, den Code effizient an die Besonderheiten und Eigenheiten der jeweiligen Hardware anzupassen. Dies erfordert eine genaue Kenntnis der Pipeline, der Scheduling-Modelle und der unterstützten Instruktionsmengen. Im Fall von XiangShan-KunMingHu-V2R2 haben die Entwickler zunächst die grundlegenden Prozessordefinitionen in LLVM integriert, wobei die Ausarbeitung des Scheduling-Modells in einem separaten, nachfolgenden Schritt erfolgt. Diese Etappe ist essenziell, um eine optimale Codegenerierung zu gewährleisten, die das volle Potential der Architektur ausnutzt. Die Einbindung des Prozessors in LLVM erfolgt durch Anpassungen in mehreren Bereichen des Projekts, einschließlich der Risikoveotrarget-spezifischen Dateien, wo Prozessormodelle beschrieben und spezifiziert werden.

Gleichzeitig wurden Tests in die Toolchains eingebaut, um sicherzustellen, dass die Unterstützung robust und fehlerfrei ist. Dabei spielt auch die Einbindung spezieller Extensions wie "ziccamoa", "zihintntl" und "zawrs" eine Rolle, die für einzigartige Funktionalitäten im XiangShan-Prozessor sorgen. Für Entwickler öffnet sich durch diese Neuerung ein breiteres Spektrum an Möglichkeiten. So können sie via LLVM nun direkt für XiangShan-KunMingHu optimieren, ohne komplexe Workarounds oder manuelle Anpassungen vornehmen zu müssen. Das ist ein erheblicher Vorteil, da der Compiler automatisch die passenden Instruktionspfade wählt und damit die Leistung sowie Energieeffizienz der resultierenden Programme verbessert werden.

Die Veröffentlichung und Pflege der dazugehörigen Dokumentation erfolgt in enger Zusammenarbeit mit der OpenXiangShan-Gemeinschaft. Das Benutzerhandbuch für KunMingHu steht öffentlich auf GitHub bereit und wird kontinuierlich aktualisiert, um Entwickler bestmöglich zu unterstützen. Darüber hinaus werden Leistungsvergleiche und Benchmarks regelmäßig in den sogenannten XiangShan Biweekly Berichten veröffentlicht, sodass Interessierte stets einen aktuellen Überblick bekommen. Die XiangShan-KunMingHu-Prozessoren gehören zu den angesehensten RISC-V-Projekten weltweit. Mit dem Fokus auf hohe Taktraten, Energieeffizienz und skalierbare Pipelines bieten sie eine attraktive Plattform für Forschung und praktische Anwendung zugleich.

Die Integration in ein etabliertes Compilerframework wie LLVM erhöht die Attraktivität zusätzlich, da in der Softwarewelt native Unterstützung für den Prozessor gewährleistet ist. Aus Sicht der RISC-V Community stellt diese Entwicklung einen großen Schritt in Richtung Standardisierung und Kompatibilität dar. Viele offene Prozessorprojekte leiden bislang unter fehlendem oder unzureichendem Compiler-Support, was die Verbreitung einschränkt. Mit XiangShan-KunMingHu und LLVM entsteht nun ein Beispiel, wie enge Zusammenarbeit zwischen Hardware-Entwicklern und Compiler-Ingenieuren den Ökosystemaufbau beschleunigen kann. Abschließend lässt sich sagen, dass die Aufnahme der XiangShan-KunMingHu-V2R2 Prozessordefinition in LLVM nicht nur eine technische Erweiterung ist, sondern auch ein Symbol für den Fortschritt der Open-Source-Hardwarebewegung.