Die Entwicklung von Netzwerktechnologien hat in den letzten Jahrzehnten enorme Fortschritte gemacht. Vor allem Ethernet-Switches spielen dabei eine zentrale Rolle für die sichere und effiziente Datenübertragung in Netzwerken aller Größenordnungen. In einer Zeit, in der Open-Source-Hardware immer stärker an Bedeutung gewinnt, stellt das Open Hardware Ethernet Switch Projekt einen faszinierenden und wichtigen Beitrag zur vernetzten Welt von morgen dar. Dieses Projekt bietet nicht nur technische Innovationen, sondern auch Offenheit und Nachvollziehbarkeit, die in der sonst oft proprietären Branche selten sind. Der Startschuss für das Open Hardware Ethernet Switch Projekt fiel bereits vor über einem Jahrzehnt, als traditionelle Hersteller nur schwer zugängliche ASICs (Application-Specific Integrated Circuits) mit vielen Einschränkungen anboten.

Die leidenschaftliche Suche nach einem geeigneten, gut dokumentierten Gigabit-Switch-Chip, der für Kleinserien oder Einzelexemplare erhältlich ist – ohne umständliche Geheimhaltungsvereinbarungen oder Mindestabnahmemengen – blieb erfolglos. Daraus entwickelte sich die Idee, auf FPGAs (Field Programmable Gate Arrays) als flexible und individuell programmierbare Plattform zu setzen. Diese Herangehensweise ermöglichte den Aufbau eines vollständig offenen Ethernet-Switches, der ohne teure und proprietäre Schaltkreise auskommt. Das erste Board, das in dieser frühen Phase des Projekts entstand, war ein komplexes und herausforderndes Design. Es setzte erstmals auf Schaltnetzteile anstelle der damals gängigen Low-Dropout-Regler (LDOs) und benutzte für die Ethernet-Verbindung RGMII-PHYs (Reduced Gigabit Media Independent Interface Physical Layer).

Diese Technologie erlaubte eine höhere Geschwindigkeit bei überschaubarem Designaufwand, erforderte aber auch fundierte Kenntnisse im Hochgeschwindigkeits-Design. Mit einer FPGA-Größe von nur etwa 15.000 Lookup-Tabellen (LUTs) und weniger als einem Megabit Speicher war der erste Entwurf rasch an seine Grenzen gestoßen. Hinzu kam, dass der Entwickler damals nur über begrenzte Messgeräte verfügte – ein 100 MHz Oszilloskop, das für Signalqualitätsmessungen bei gigabitfähigen Ethernet-Schnittstellen nicht ideal war. Trotz der Herausforderungen gelang es, einige der PHY-Ports erfolgreich in Betrieb zu nehmen.

Doch das Projekt zeigte deutlich, dass eine umfassende Realisierung eines modularen, mehrportigen Switches mit externer CPU-Unterstützung und einem umfassenden Speichermanagement mehr Know-how, bessere Tools und größere FPGA-Kapazitäten erfordert. Das erste Board war kein vollwertiger Erfolg, doch es legte den Grundstein für die weiteren Entwicklungen und half, wichtige Erfahrungen zu sammeln. In den Folgejahren konzentrierte sich der Entwickler auf den Ausbau seiner Fähigkeiten im digitalen RTL-Design und auf den Erwerb besserer Messtechnik. Die Anschaffung eines leistungsstärkeren Oszilloskops, eines 350 MHz Teledyne LeCroy WaveSurfer 3034, ermöglichte erstmals Signalqualitätsanalysen für RGMII-Verbindungen und das Protokoll-Decoding auf 100BASE-TX-Ebene. Die Vision eines zukünftigen Zehn-Gigabit-Ethernet-Switches führte zu weiteren ambitionierten Projekten, wie dem Versuch, ein 10 GHz Sampling-Oszilloskop namens FREESAMPLE zu entwickeln.

Zwar wurde dieses Projekt vorerst auf Eis gelegt, doch es brachte wertvolle neue Perspektiven für die Signal- und Messtechnik mit sich. Mit wachsender Erfahrung wandelte sich der Fortschritt des Switch-Projekts von einem einfachen Gigabit-Switch hin zu einer modularen, hochskalierbaren Plattform, die große Stückzahlen und anspruchsvolle Netzwerkfunktionen abbilden kann. Das Konzept eines erweiterten Netzwerksystems namens LATENTx entstand dabei. Dieser Name fungierte als Oberbegriff für eine Familie von Netzwerkgeräten, die farblich gekennzeichnete Subprojekte trennen sollten. Geplant war, zunächst einen Gigabit-Edge-Switch mit 24 Ports (LATENTRED) und später einen 10-Gigabit-Core-Switch (LATENTORANGE) zu entwickeln.

Durch die hohen Anforderungen an die Portanzahl stellte die Wahl des PHY-Interfaces eine besondere Herausforderung dar. RGMII mit seinem parallelen 4-Bit-Datenbus pro Richtung erfordert zahlreiche Pins und sorgt dadurch für komplexe Leiterplattenlayout-Herausforderungen. SGMII (Serial Gigabit Media Independent Interface) hingegen, mit seinen differenziellen Signalen für TX und RX, reduzierte diesen Aufwand signifikant. Allerdings blieb noch immer eine beträchtliche Anzahl von Pins für 24 Ports übrig. Ein entscheidender Wendepunkt im Projekt war die Einführung der QSGMII-Technologie (Quad Serial Gigabit Media Independent Interface), repräsentiert durch den VSC8512-Phy von Vitesse, nun Teil von Microchip.

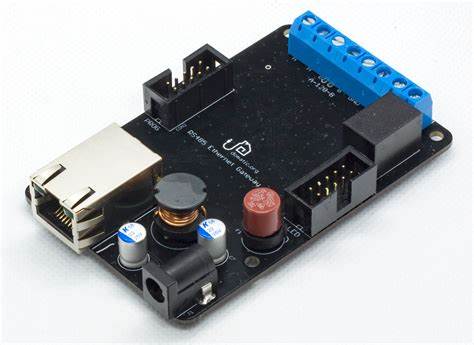

Dieser Baustein ermöglicht es, vier Gigabit-Ports über eine einzige SGMII-Verbindung aufzuschalten, was die Anzahl der benötigten Hochgeschwindigkeitsleitungen drastisch reduziert. So wurden nicht mehr 24 einzelne SGMII-Links erforderlich, sondern nur noch sechs QSGMII-Lanes – ein Meilenstein in der Kosten- und Komplexitätsreduktion. Das daraus entstandene LATENTPINK-Modul kombinierte einen VSC8512-QSGMII-PHY mit zwei TI DP83867-SGMII-PHYs, um insgesamt 14 Gigabit-Ports bereitzustellen. Zusätzlich verfügte die Plattform über einen 10 GbE SFP+ Uplink sowie einen dedizierten RGMII-Management-Port für Steuerzwecke. Der Übergang zu einem komplexeren 8-lagigen Leiterplattendesign und die Integration moderner Murata-Module sowie FPGA-Transceiver zeigten das Streben nach professioneller Fertigungsqualität und zukunftsweisender Technik.

Die Steuerung des Systems erfolgte per STM32H7-Mikrocontroller über ein Quad-SPI-Interface, während die eigentliche Switching-Logik auf einem Xilinx FPGA der 7er-Serie (XC7K160T) basierte. Obwohl das Board funktionell war und die Weiterleitung von Paketen sowie VLAN-Unterstützung bot, waren Einschränkungen bei der verfügbaren FPGA-Ressourcen noch spürbar. Die notwendige Komplexität für einen 24-Port-Switch mit internen Puffern und einem verteilten Forwarding-Mechanismus konnte auf dem kleinen FPGA nicht mehr effizient umgesetzt werden. Vor allem die Architektur des Switching-Fabric stellte hohe Anforderungen an Speicher und Logikressourcen. Die Nutzung externer QDR-II+ SRAM als Paketpuffer war elegant, brachte jedoch Herausforderungen bei der Registerverwaltung und dem integrierten Datenbus mit sich.

Verschiedene proprietäre Busstrukturen für Steuer- und Datenebene führten zu Komplikationen, die bei einem nächsten Design verbessert werden sollten. Parallel dazu erweiterte der Entwickler sein Toolset, insbesondere mit eigenem Protokoll-Decoder-Support für verschiedenste Ethernet-Standards von 10/100 bis 10G und der Entwicklung modularer Software für die Mess- und Steuerungseinheiten, wie „ngscopeclient“. Verbesserungen bei der EM-Simulation durch Software wie Sonnet und der Zugang zu besseren Oszilloskopen rundeten die technische Basis für das Projekt ab. Der Sprung zu leistungsfähigeren FPGAs markiert eine neue Entwicklungsphase. Während die Xilinx 7er-Serie lange das Rückgrat bildete, störten Limitierungen bei Pinanzahl, Logikkapazitität und Preis die Skalierbarkeit.

So wurde das Augenmerk auf neuere UltraScale+ Modelle wie den XCKU5P gelegt, der mit etwa 216.000 LUTs, 16 Hochgeschwindigkeits-Transceivern und hohem Speicherangebot ein erhebliches Upgrade darstellt. Nicht zuletzt spielte auch der günstige Zugang zu salvaged Boards und Chips eine wirtschaftliche Rolle. Die geplante Architektur des LATENTRED-Switches sieht nun eine 1U-Höheneinheit mit zwei 24-Port Line Cards vor, die jeweils mit doppeltem VSC8512 ausgestattet sind. Zusätzlich sind duale 10/25G SFP28 Uplinks vorgesehen.

Dies ermöglicht eine enorm skalierbare und leistungsstarke Plattform, die zukünftigen Anforderungen in Rechenzentren und Unternehmensnetzwerken gerecht werden soll. Die Verbindung zwischen den Komponenten erfolgt über modernste Hochgeschwindigkeits-Interconnect-Technologien wie die Samtec ARC6 Steckverbinder und Twinax-Kabel, die Signalqualität bis zu 32 Gbps unterstützen und somit auch für zukünftige Erweiterungen flexibel sind. Dies entlastet das PCB-Design von langen umständlichen Leitungswegen und senkt Fertigungskosten. Der Switch-Engine-Board selbst ist derzeit noch in Planung und Entwicklung. Die angestrebte Schaltmatrix besteht aus einem 4x4 64-Bit Crossbar mit 400 MHz Takt, was eine theoretische Gesamtbandbreite von über 100 Gbps bietet.

Diese Art von Architektur garantiert niedrige Latenzen und effiziente Weiterleitung, die für moderne Switches unerlässlich ist. Auf Firmware-Ebene wurde bereits eine Portierung des 10G Ethernet MAC/PCS auf AXI4-Stream erfolgreich umgesetzt, und die Arbeiten an den 1G-Komponenten sind ebenfalls weit fortgeschritten. Die geplante Integration von VLAN-Tagging, MAC-Adresstabellen und Fehlerkontrollen sind wichtige Bausteine für ein vollständiges Produkterlebnis. Zusammenfassend zeigt das Open Hardware Ethernet Switch Projekt, wie durch beharrliches Engagement, technische Innovation und den Einsatz moderner Technologien ein konkurrenzfähiges Netzwerkgerät mit offenem Design entstehen kann. Dies ermöglicht es nicht nur Entwicklern und Forschern, tief in die Funktionsweise moderner Switches einzutauchen, sondern legt auch den Grundstein für eine neue Ära von Netzwerkinfrastruktur, die offen, flexibel und wartbar ist.

Die Zukunft des Projekts verspricht spannende Weiterentwicklungen mit Potential für leistungsstarke, kosteneffiziente und skalierbare Lösungen. Mit dem Fokus auf 25 GbE und darüber hinaus erweist sich das Open Hardware Ethernet Switch Projekt als visionärer Wegbereiter in der Open-Source-Hardware-Community und der Netzwerktechnologie insgesamt.