In der heutigen Ära moderner Mehrkernprozessoren und paralleler Verarbeitungssysteme ist das Verständnis von Speicher-Konsistenzmodellen von entscheidender Bedeutung für Entwickler, Systemarchitekten und Wissenschaftler. Speicher-Konsistenzmodelle bestimmen, wie simultan laufende Threads oder Prozesse den Zustand des gemeinsamen Speichers wahrnehmen und interpretieren. Diese Wahrnehmung beeinflusst direkt die Korrektheit und Leistung paralleler Programme. Die Herausforderung dabei ist weniger die reine Parallelität, sondern vielmehr die Ordnung, in der Speicheroperationen gesehen und ausgeführt werden. Die Ordnung von Operationen in einem System mit mehreren Ausführungseinheiten ist komplex.

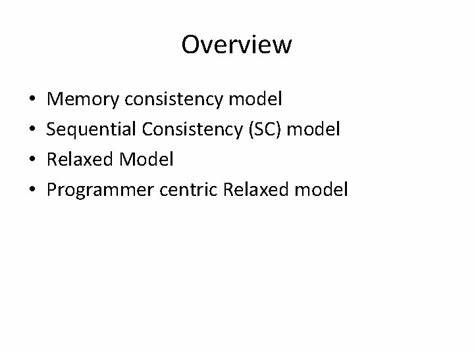

Intuitiv scheint es logisch, dass alle Aktionen strikt in der Reihenfolge ablaufen, in der sie programmiert wurden – sowohl innerhalb eines einzelnen Threads als auch zwischen den Threads. Dies nennt man die Idee der sequentiellen Konsistenz, die als eine Art Goldstandard betrachtet wird. Sequentielle Konsistenz bedeutet, dass die Ergebnisse eines parallelen Programms so erscheinen, als ob alle Operationen in einer bestimmten globalen Reihenfolge ausgeführt wurden, wobei die Befehle innerhalb eines einzelnen Threads in Programmreihenfolge bleiben. Doch trotz ihrer intuitiven Natur bringt das Modell der sequentiellen Konsistenz erhebliche Leistungseinbußen mit sich. Die Herausforderung bei modernen Mehrkernprozessoren besteht darin, schnelles und effizientes Arbeiten mit Speicherzugriffen zu ermöglichen, wobei dennoch ein korrektes Verhalten erhalten bleibt.

Die Tatsache, dass Hardwarekomponenten und Optimierungen wie Cache-Hierarchien und Store-Buffer eingesetzt werden, erschwert die strikte Einhaltung der sequentiellen Konsistenz. Ein zentrales Konzept in der Speicherhierarchie moderner CPUs ist die sogenannte Kohärenz. Kohärenz garantiert, dass alle Speicherzugriffe auf dieselbe Speicheradresse von allen Prozessen in derselben Reihenfolge gesehen werden – das heißt, es gibt immer einen „einzigen Gewinner“ bei Mehrfachbeschreibungen eines Speicherortes. Kohärenz sichert auf diese Weise, dass niemand plötzlich einen veralteten Wert liest, wenn mehrere Threads gleichzeitig schreiben. Andererseits ist es nicht zwingend notwendig, dass alle Operationen auf verschiedene Speicheradressen strikt strikt sequentiell konsistent sein müssen.

In der Praxis führen diese Anforderungen oft zu unnötigen Latenzen, da Prozessoren gezwungen wären, auf langfristige Synchronisationen zu warten, bevor sie mit den nächsten Anweisungen fortfahren können. Um die Performance zu erhöhen, haben Prozessorhersteller daher im Laufe der Zeit schwächere Speicher-Modelle eingeführt. Ein Beispiel hierfür ist das Total Store Ordering-Modell, oder TSO. TSO akzeptiert, dass es temporäre Verzögerungen bei der Sichtbarkeit einer Speicheroperation für andere Threads geben kann, indem es Speicheroperationen in Puffern zwischenlagert. So kann eine Schreiboperation schneller abgeschlossen und die darauffolgende Leseoperation unmittelbar ausgeführt werden, ohne auf die vollständige Aktualisierung des globalen Speichers zu warten.

Die Spannung zwischen der Programmierbarkeit und der Performance zeigt sich darin, dass TSO gewisse Ausgabemuster erlaubt, die bei streng sequentieller Konsistenz unmöglich wären – dies kann zu unerwarteten Programmverhalten führen, welche Entwickler sorgsam berücksichtigen müssen. Diese Entspannung der Speicherordnung nimmt bei vielen Architekturen weiterhin zu. Während x86-basierte Systeme zumindest eine relativ starke Konsistenzhaltung besitzen, implementieren viele andere Architekturen, wie etwa ARM, deutlich schwächere Modelle. Hier sind fast alle Arten von Operationen und deren Reihenfolgen von den Hardwareoptimierungen betroffen. Die Folge ist eine enorme Optimierungsfähigkeit der Prozessoren, gepaart mit einer deutlich komplexeren Programmier- und Verifizierungsarbeit.

Um mit den Komplexitäten schwacher Speicher-Modelle umzugehen, bieten moderne CPUs Mechanismen an, die durch Synchronisationsanweisungen oder Speicherbarrieren kontrolliert werden können. Diese Anweisungen stellen temporär eine sequentielle Konsistenz an bestimmten Programmstellen sicher und sind unerlässlich, um Korrektheit bei geteiltem Speicher sicherzustellen. Allerdings sind Speicherbarrieren teuer in ihrer Ausführung und sollten deshalb sparsam eingesetzt werden. Ebenso wichtig wie die Hardware-Sicht auf Speicher-Modelle ist die Ebene der Programmierung und Übersetzung. Compiler optimieren Programme aggressiv und führen dabei oft Umordnungen von Speicherzugriffen durch, um effizienteren Code zu erzeugen.

Ohne eine klar definierte Speichermodellierung auf Sprachebene könnten solche Optimierungen zu unerwartetem Verhalten führen, besonders bei parallelen Programmen. Moderne Programmiersprachen wie Java und C++ haben deshalb eigene formalisierte Speicher-Modelle eingeführt, um sowohl die Erwartungen der Entwickler zu erfüllen als auch die zugrundeliegenden Optimierungen kontrolliert zu ermöglichen. Ein häufiges Problem in paralleler Programmierung ist das sogenannte Datenrennen. Datenrassen treten auf, wenn mehrere Threads ohne geeignete Synchronisation auf denselben Speicherzugriff zugreifen und mindestens einer davon schreibt. In diesen Fällen wird häufig unvorhersehbares Verhalten erzeugt, da Speicheroperationen von den zugrunde liegenden Hardware- oder Compileroptimierungen unterschiedlich wahrgenommen werden können.

Sprachen mit definierten Speicher-Modellen bieten in der Regel die Garantie, dass Programme ohne Datenrennen ein sequentiell konsistentes Verhalten zeigen werden – was die Entwicklung sichererer paralleler Programme erheblich erleichtert. Der pragmatische Umgang mit Speicher-Konsistenz bedeutet für Entwickler in der Praxis, geeignete Synchronisationsmechanismen, Libraries und Abstraktionen zu verwenden, um Sicherheitslücken und unerwartete Parallelitätsfehler zu vermeiden. Die zugrundeliegenden Hardware-Aktionen und die Speicherhierarchie werden durch Betriebssysteme und Laufzeitbibliotheken verwaltet, die so konzipiert sind, dass sie Komplexität abstrahieren und gleichzeitig eine akzeptable Performance gewährleisten. Insgesamt hat die Forschung und Entwicklung der letzten Jahrzehnte gezeigt, dass es keinen universellen Speicher-Konsistenzansatz geben kann, der sowohl maximale Performance als auch intuitive Programmierbarkeit perfekt balanciert. Vielmehr bewegt sich die Branche zwischen den Extremen, bietet starke Konsistenz dort, wo es gebraucht wird, und erlaubt flexiblere, performantere Modelle dort, wo es möglich ist.

Das Bewusstsein für diese komplexen Zusammenhänge ist der erste Schritt, um robuste, effiziente und skalierbare parallele Software zu entwickeln. Wer sich mit Speicher-Konsistenzmodellen beschäftigt, kann die Tiefen moderner Computerarchitektur besser verstehen und sicherer in der Herstellung von zuverlässigen Mehrkern-Programmen navigieren – und damit auch in der zunehmend vernetzten und parallelen Welt von morgen erfolgreich sein.

![GitHub Helping Users Work Together (2013) [video]](/images/606033DB-4397-4F1A-B8B9-F94CA1699256)